ZEPマガジン

|

2025年10月17日号

[FPGA/HDL/論理回路][AI/IoT/マイコン]

コンピュータのメカニズム データ転送のしくみ CPUは計算や制御の中心であり、各種記憶素子や周辺機能とデータをやり取りする役割を担う |

|

2025年10月16日号

[アナログ/センサ/計測][半導体/電子部品][AI/IoT/マイコン]

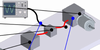

MOSFETはマイコンで直駆動できない 4Aゲート・ドライバでPWM駆動してみた MOSFETのゲートは電荷を蓄える容量性負荷であり,ON/OFFのたびに大きな電流を必要 |

|

2025年10月15日号

[アナログ/センサ/計測][半導体/電子部品][AI/IoT/マイコン]

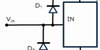

IC入力端子を守る2つの保護ダイオード 過電圧は電源とグラウンドへスルー・パス アナログICやディジタルICは,入力電圧の範囲が電源電圧から0Vまでに制限されている.入力端子に過大な電圧が加わると,内部のトランジスタが壊れる |

|

2025年10月14日号

[アナログ/センサ/計測][半導体/電子部品][AI/IoT/マイコン]

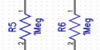

教科書が教えてくれない抵抗値選び E12系列を使う!同じ抵抗値で揃える! 抵抗値の選定は,増幅率や分圧比に直接影響する.単純な計算だけでなく,実際の回路設計では,E12系列の抵抗を使うなど,入手性やコストも考慮する |

|

2025年10月13日号

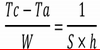

[ノイズ/放熱対策][シミュレータ/ツール]

強制?自然?筐体放熱?密閉筐体の熱計算 密閉筐体での放熱設計の基本 小型密閉筐体に15W程度の基板を実装する場合,部品から発生する熱を効率的に筐体へ逃がすことが重要 |

|

2025年10月12日号

[電源/電池/パワエレ][AI/IoT/マイコン][信号処理/セキュリティ]

高速×並列処理!電源制御マイコンの要件 CPU/DSP/EPU搭載のMD6605を例に モータでは50μs程度の制御レートで十分だが,電源では0.5μ~2μsの応答が必要.単一のCPUやDSPではなく,並列処理に対応したマルチコアCPUがよい |

|

2025年10月11日号

[ノイズ/放熱対策][シミュレータ/ツール]

クルマ向け超低硬度TIM:大型電子部品の放熱 形状さまざま!インダクタやキャパシタの冷却 筐体との接触面が不均一になる凹凸のある電子部品には,超低硬度TIMを活用すれば,柔らかいシートが部品表面に密着し,効率的に熱を筐体に伝達できる |

|

2025年10月10日号

[電源/電池/パワエレ][シミュレータ/ツール][ノイズ/放熱対策]

電子回路シミュレータLTspiceでCISPLE試験 インバータ/配線/LISN/負荷をモデリング CISPR規格に基づく伝導エミッション評価を回路シミュレータで模擬すると,実機測定前に問題点を把握できる |

|

2025年10月9日号

[電源/電池/パワエレ][制御/モデルベース設計][シミュレータ/ツール]

高効率化したいなら!不連続モードは重要な選択肢 不連続モードで高効率を狙った昇圧コンバータ スイッチング電源は,周期一定で臨界点近傍の動作を維持すれば,不連続領域でも安定な制御が可能であり,制御回路を複雑化せずに高効率が得られる |

|

2025年10月8日号

[ノイズ/放熱対策][基板/実装/3Dプリンタ]

2種類の電流 差動と同相 「2種類の電流 差動と同相」の解説ページです 高周波信号や大電流のスイッチングが混在する環境では,不要な電磁放射が問題になる.注目すべきは「差動モード電流」と「同相モード電流」という2種類の電流が流れること |

|

2025年10月7日号

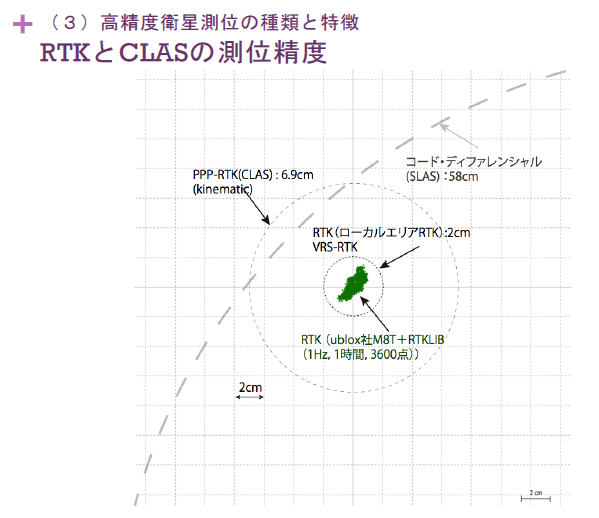

[ロボット/自動運転/宇宙]

CLAS vs RTK 測位精度比べ 単独高精度測位 みちびき補正信号CLAS入門 数cmレベルの衛星測位技術の代表的な方式といえば「RTK(Real Time Kinematic)」と「CLAS(Centimeter Level Augmentation Service)」.両者の違いは? |

|

2025年10月6日号

[ノイズ/放熱対策][基板/実装/3Dプリンタ]

30kV/cm と覚えよう 空気が絶縁破壊する電界強度 標準温度と標準気圧において,空気が絶縁破壊して電気的導体となる電界強度は約30kV/cm.これを超える電界が加わると,空気分子が電離して電子が流れ,放電現象が生じる |

|

2025年10月5日号

[ノイズ/放熱対策][基板/実装/3Dプリンタ]

間接ESDはリセット信号の直列抵抗で対策 デシベルから始めるプリント基板EMC マイクロプロセサのリセット信号は低速でありながら高感度な入力であるため,わずかなノイズで誤動作する.有効な対策は,リセット信号ラインへの直列抵抗の追加 |

|

2025年10月4日号

[ノイズ/放熱対策][基板/実装/3Dプリンタ]

片面より両面有利!サーマル・ビアの熱分散効果 TO252パッケージで計算してみた 片面基板は,放熱パッドの面積が大きくても裏面に銅箔がないため熱が拡散しにくい.両面基板は,表面の放熱パッドと裏面の銅箔が熱を分散する経路を形成する |

|

2025年10月3日号

[ノイズ/放熱対策][基板/実装/3Dプリンタ]

放熱フィン数の最適解 多すぎても性能が出ない ヒートシンクのフィンを増やすことで表面積は増すが,間隔が狭くなると風の流れが阻害され,逆に熱抵抗が増加する |

|

2025年10月2日号

[ノイズ/放熱対策][基板/実装/3Dプリンタ]

大電力素子の放熱術 TIM経由筐体と冷媒伝搬・空冷 目標熱抵抗が1K/W以下の発熱量の大きい大電力デバイスは,ヒートシンクやファンを組み合わせて熱を効率的に外部に逃がす必要がある |

|

2025年10月1日号

[ノイズ/放熱対策][基板/実装/3Dプリンタ]

基板の熱設計複雑な計算はExcelで 転ばぬ先の杖熱源と経路を事前計算 複数の熱源がある基板上での熱分布は各部品の発熱量,表面からの放熱条件に依存し,温度によって放熱率が変わるため,連立方程式を解く必要があり,手計算では解析が困難 |

|

2025年9月30日号

[ノイズ/放熱対策][基板/実装/3Dプリンタ]

放熱設計の第1歩部品単体の熱抵抗管理 放熱器?水冷器?早期検討が成功の鍵 熱対策は,まず部品単体の熱抵抗を理解することから始まる.単体熱抵抗とは,部品自身がもつ冷却能力を示す指標 |

|

2025年9月29日号

[ノイズ/放熱対策][基板/実装/3Dプリンタ]

クルマやスマホの筐体放熱術 部品上面接触,基板裏面接触,部品の反転取付 筐体を熱経路として活用する方法が広く用いられている.放熱経路は部品上面,基板裏面,部品の反転取付の3種類 |

|

2025年9月28日号

[ノイズ/放熱対策][基板/実装/3Dプリンタ]

拡がり熱抵抗と接触熱抵抗に注目 放熱器設計の基本 小形部品は,ヒートシンク・ベース上で温度差が生じやすい.ヒートシンク・ベースを厚くしたり,熱伝導性の高い材料を使って拡がり熱抵抗を低減するべき |