JESD伝送路はRFセンスで設計する

計測のためのA-Dコンバータ実装術

JESD伝送路の設計基礎と差動伝送

|

|---|

|

図1 JESDインターフェースの評価試験は,FPGAや各種ソフトウェアに組み込まれたサポート機能を用いて実施する.画像クリックで動画を見る.または記事を読む.[著]藤森 弘己

詳細:[VOD]高速&エラーレス!5G×EV時代のプリント基板&回路設計 100の要点 |

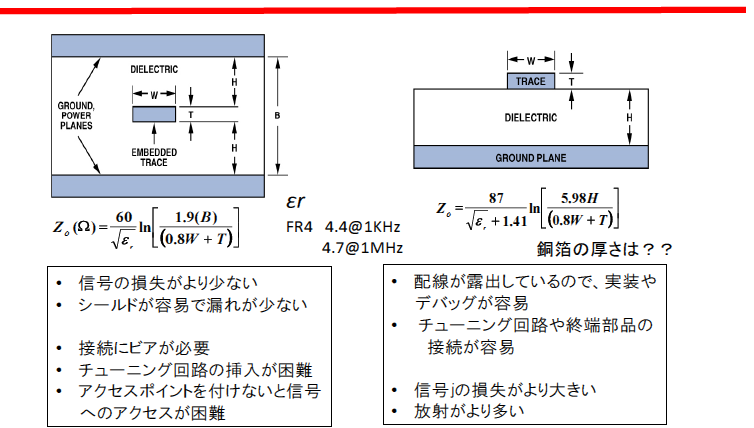

JESD伝送路は差動伝送を前提としており,ストリップ線路やマイクロストリップ線路が使われます. これらは表面実装で設計され,50$\Omega$の差動ペアが合わせて100$\Omega$になるようなパターンを形成します.

JESD204のCML信号レベルはすべて作動信号で,USBの作動信号と同様です. この設計はCADシステムのレイアウト機能によって自動的に処理されることが多いです. シミュレータでも計算式に基づく評価が可能で,設計者はこれを目安に活用するとよいです.

信号伝送速度とタイミング調整の重要性

ストリップ線路やマイクロストリップ線路の伝送速度は,電気信号のパターンが伝わる速度に大きく影響します. 1GHzは1周期が1nsに相当し,1Gbpsのパルス幅も約1nsです. 10Gbpsでは100ps,30Gbpsではさらに1/3程度の数十ps単位となり,信号は数cmの範囲で高速に進みます.

こうした高速なタイミングの早い遅いを正確にチューニングし,設計に反映させることが不可欠です. ps単位の時間遅延が伝送長さに対応し,何mの配線長が何psの遅延を生むかを理解することが重要です.

レイアウト設計とFPGA・コンバータのタイミング調整

JESD204の伝送路設計でもっとも重要で時間を要するのは,配線設計そのものよりもコンバータやFPGAにおけるタイミング調整です. 最新の高速JESDコンバータには,数ps単位でタイミングを微調整するためのレジスタが多数内蔵されています.

データシートや計算上ではタイミングが合っていても,実際にビット・エラーが生じる場合はこうしたレジスタによる微調整が必要です. 単純な基板設計では問題が少ないですが,複雑なシステムほど調整は難しくなります.

基板上では信号のタイミングを合わせるために,途中で信号経路を遠回りさせて遅延調整する工夫も行われます. 50$\Omega$の同軸ケーブルをとおり,FR4基板上で信号が伝達されますが,それでも1GHz以下の信号特性は保たれています.

- 差動伝送に適したストリップ線路・マイクロストリップ線路の設計

- 信号のパルス幅と伝搬速度に基づくps単位のタイミング管理

- FPGA・コンバータの内蔵レジスタを用いた微調整の重要性

著者紹介

- 1979年 芝浦工業大学 通信工学科卒業

- 同年 Analog Devices of Japan Inc に入社(後にアナログ・デバイセズ株式会社)同社にてアナログ・モジュール開発,Mixedシグナル・テスタのテスト・モジュール開発、高速リニア・カスタム集積回路の開発サポート,汎用リニア製品マーケティング等を担当.

著書

- OPアンプ増幅回路の2つのゲイン,ZEPエンジニアリング株式会社.

- [VOD]高速&エラーレス!5G×EV時代のプリント基板&回路設計 100の要点,ZEPエンジニアリング株式会社.

- [VOD]アナログ・デバイセズの電子回路教室【差動信号とその周辺回路設計技術】,ZEPエンジニアリング株式会社.

- [VOD]アナログ・デバイセズの電子回路教室【A-D/D-Aコンバータの使い方】,ZEPエンジニアリング株式会社.

- [VOD]Before After!ハイパフォーマンス基板&回路設計 100の基本【パワエレ・電源・アナログ編】/【IoT・無線・通信編】,ZEPエンジニアリング株式会社.

参考文献

- [VOD]Before After!ハイパフォーマンス基板&回路設計 100の基本【パワエレ・電源・アナログ編】/【IoT・無線・通信編】,ZEPエンジニアリング株式会社.

- [VOD]高精度アナログ計測回路&基板設計ノウハウ,ZEPエンジニアリング株式会社.

- [VOD]Gbps超 高速伝送基板の設計ノウハウ&評価技術,ZEPエンジニアリング株式会社.

- [VOD]事例に学ぶ放熱基板パターン設計 成功への要点,ZEPエンジニアリング株式会社.

- [VOD/KIT]GPSクロック・ジッタ・クリーナ,ZEPエンジニアリング株式会社.

- [Book]電子回路とプリント基板のノイズ解決 即答200,ZEPエンジニアリング株式会社.