16ピンDIP FPGAのHDLコーディング環境

作る!私のDIPコンピュータ

|

|---|

| Quartus Prime Lite Editionをインストールし,BlinkLEDプロジェクトを作成する手順を解説し,RTLを作成してFPGAに設定する方法を説明する 〈著:圓山 宗智〉 |

| 【PR:3月21日開催】:[Onsite/Full KIT/data]復刻!インテル4004プロセッサとビジコン社電卓141-PF |

| 画像クリックで動画を見る.または記事を読む |

16ピンDIP FPGAのHDLコーディング環境構築

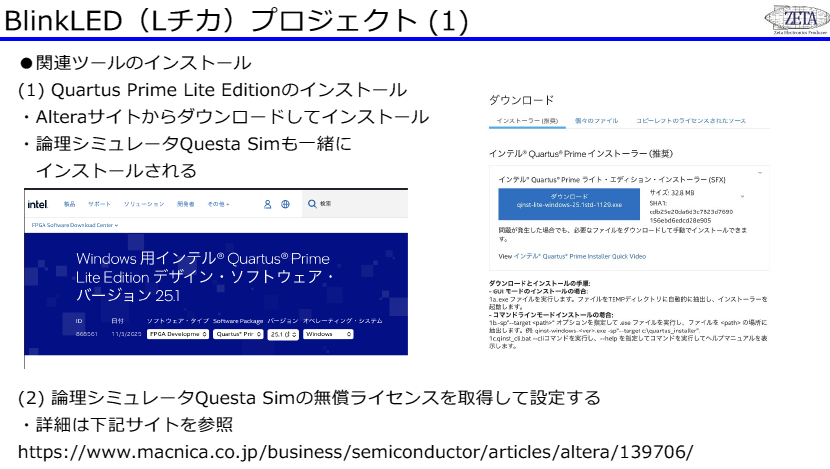

16ピンDIPパッケージのFPGAを用いたHDLコーディング環境を構築するには,まずQuartus Prime Lite Editionをインストールします.Alteraの公式サイトから入手可能で,インストール時に論理シミュレータのQuesta Simも同時に導入されます.Questa Simを利用する際は無償ライセンスの取得と設定が必要です.詳細は専門サイトを参照してください.

次にQuartus Primeでプロジェクトを新規作成します.FileメニューからNew Project Wizardを開き,作業ディレクトリやプロジェクト名,トップレベルデザイン名を設定します.プロジェクトタイプはEmpty Projectを選択し,特にファイルの追加は行いません.デバイスは10M02DCV36C8Gを指定し,EDAツール設定はデフォルトのままとします.プロジェクト作成後,AssignmentsメニューのDevice設定で「Enable JTAG pin sharing」をオンにすることが重要です.これによりJTAG端子とFPGAのピンを共有できます.

RTL設計とプロジェクト設定のポイント

プロジェクト内にBlinkLED用のRTLコードを作成するため,BlinkLEDディレクトリの下にRTLフォルダを作成します.SystemVerilogで記述したtop.svファイルをこの中に配置します.設計では55MHzの内蔵発振器をクロック源に使用し,パワーオンリセット信号を生成する回路を実装します.リセット信号por_nとカウンタpor_countはFPGA制約設定で初期値を0に設定しておきます.

LED点滅制御はカウンタled_countが一定カウントに達したときにLED出力をトグルし,カウンタをクリアするしくみです.JTAGピン共有のため,LED信号はC1ピン(TDI)に割り当て,そのほかのJTAG共有端子はダミー信号として扱い,適切に入力・出力設定しています.ダミー端子は未使用信号として論理的に処理され,出力は固定値を割り当てます.

コンパイルからFPGA書き込みまでの手順

内蔵発振器はIP CatalogからInternal Oscillatorを選択して追加します.プロジェクト設定でtop.svとOSC.qsysをファイルに追加し,SystemVerilog入力を有効化します.これらの設定後,仮合成を実行してエラーがないことを確認します.

ピン・アサインはPin Plannerで行い,LEDをC1ピン,ダミー信号をそれぞれC3,D3,D2ピンに割り当てます.パワーオンリセット用ノードの初期化はAssignment Editorでpor_nとpor_counterをPower-Up Levelに設定し,値をLowにします.タイミング制約ファイルはBlinkLEDのような簡単な設計では必須ではありませんが,必要に応じて作成し追加可能です.

最終的にProcessingメニューからコンパイルを再実行し,問題がなければFPGAの書き込み準備が整います.DIP_FPGA本体とライタをJTAG信号および電源で接続し,USBケーブルでPCと接続します.本体上に磁石を置き,Programmerを起動してJTAG接続を確認します.output_filesフォルダ内のFPGA.sofファイルを選択し,SRAMへの書き込みを行います.成功後はFPGA.pofファイルを選択してFLASHメモリへの書き込みを行い,設定を完了します.

〈著:ZEPマガジン〉参考文献

- [VOD/KIT/data]新人技術者のためのRISC-V CPU設計 初めの一歩,ZEPエンジニアリング株式会社.

- [VOD/KIT]一緒に動かそう!Lチカから始めるFPGA開発【基礎編&実践編】,ZEPエンジニアリング株式会社.

- [VOD/KIT]Xilinx製FPGAで始めるHDL回路設計入門,ZEPエンジニアリング株式会社.

- [VOD/KIT]Zynqで初めてのFPGA×Linux I/O搭載カスタムSoC製作,ZEPエンジニアリング株式会社.

« ZEPマガジン前の記事「DFP?UFP?USBの基礎用語」