超高スルーレートのSiC/GaNを安全に使う

SiC GaN FETの高速ドライブ回路設計

|

|---|

| シリコンMOSFETは高いスルーレートを実現するが,特にSICデバイスではソース端子の分割が重要であり,回路設計時には電流経路の干渉を避ける工夫が必要である 〈著:住谷 善隆〉 |

| 【出典】:[VOD]小型&高出力!高効率電源設計のためのSiC/GaNトランジスタ活用 100の要点 |

| 画像クリックで動画を見る.または記事を読む |

SiC/GaN FETの高速スルーレートと安全性

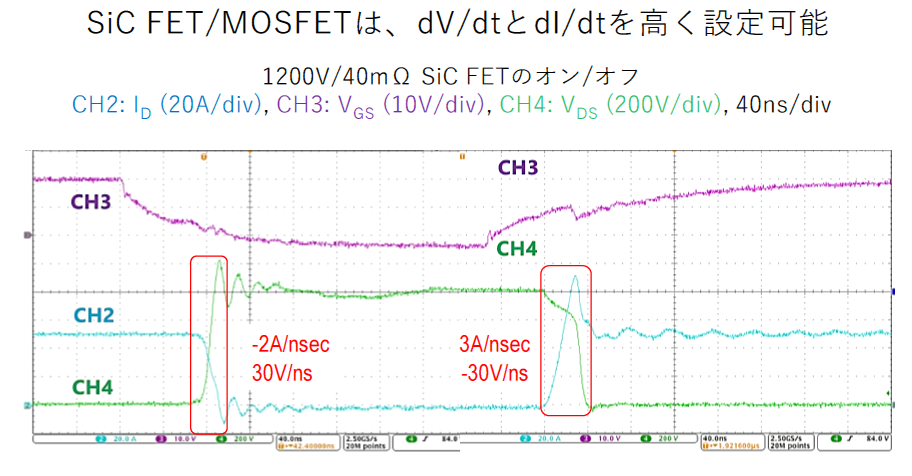

SiCやGaNを用いたパワー半導体はシリコンMOSFETに比べて非常に高いスルーレートを実現可能です.スルーレートとは電圧変化の速度を示し,高速なスイッチング動作に寄与します.これにより効率向上や小型化が期待できますが,高スルーレートを安全に扱うためには独特の注意点があります.特にSiCデバイスはパッケージ構造がシリコンMOSFETと異なり,ソース端子が複数にわかれていることが特徴です.

この構造はコモンソースインダクタンスの影響を低減するために設計されています.具体的には,ゲート駆動用の電流経路とパワー・トランジスタのメイン電流経路を分離することで,それぞれの干渉を防止しています.GaNデバイスではスレッショルド電圧が低いため,この配慮が特に重要です.回路設計時にはこの端子分割の意味を理解し,適切に配線する必要があります.

キャルベンソース端子の役割と注意点

SiCデバイスのソース端子は「キャルベンソース端子」と「ソース端子」にわかれています.キャルベンソース端子はゲート駆動用であり,ドレイン電流を流すことはできません.データシートには必ずその旨の注意書きが記載されています.内部構造を詳しく見ると,キャルベンソース端子のボンディングワイアーは細く,抵抗値が高いため大電流には耐えられません.逆にソース端子側は太い電極やクリップで構成されており,大電流を流すことが可能です.

この特性を踏まえ,フライバックコントローラ等でのカレントセンス回路設計も工夫が必要です.キャルベンソース端子に抵抗を挿入し,ゲート間とソース・ドレイン間の電流経路を分離する方法が推奨されています.これによりピーク電流を抑制し,安定した動作を確保できます.

パッケージ設計と実装上の注意点

SiCデバイスの高速スルーレートはリード端子の長さにも影響を与えます.従来はリードが長くても動作に問題がなかったものの,高スルーレート環境ではできるだけリードを短くすることが求められます.リードの曲げ作業も注意が必要で,専用ジグを用いて太い電極部分を保持しながら曲げる必要があります.無理な曲げはボンディングワイアーの断線やディラミネーションを引き起こし,湿度の侵入や電気特性の劣化を招きます.

さらに高電圧用途ではパッケージの絶縁構造にも注意が必要です.絶縁タイプと非絶縁タイプがあり,絶縁タイプはセラミックプレートで一度絶縁してから基板に接合します.非絶縁タイプは直接高熱パッドに接続されます.用途や評価条件に応じて適切なタイプを選択しなければなりません.

面実装パッケージでは沿面距離の確保がトレンドです.標準的な10×15mmパッケージで約4.75mmの沿面距離が確保されていますが,1000Vを超える高電圧用途では不足する場合があります.この場合,放熱パッドの面積を小さくして沿面距離を延ばした高圧対応パッケージが利用されます.高電圧回路設計時は沿面距離を含めたパッケージ仕様の検討が不可欠です.

〈著:ZEPマガジン〉参考文献

- [Onsite/KIT/data]トランス製作実習!スイッチング電源回路設計&シミュレーション,ZEPエンジニアリング株式会社.

- [VOD]小型&高出力!高効率電源設計のためのSiC/GaNトランジスタ活用 100の要点,ZEPエンジニアリング株式会社.

- [VOD]Before After!ハイパフォーマンス基板&回路設計 100の基本【パワエレ・電源・アナログ編】/【IoT・無線・通信編】,ZEPエンジニアリング株式会社.

- [VOD/KIT/data]一緒に作る!LLC絶縁トランス×超高効率・低雑音電源 完全キット,ZEPエンジニアリング株式会社.

- [VOD/KIT/data]実験キットで学ぶ 電源・アナログ回路入門,ZEPエンジニアリング株式会社.

« ZEPマガジン前の記事「計測のための24ビット$\Sigma\Delta$型A-Dコンバータ活用[第3回:低ノイズA-D変換システムの設計]」