Access:222

自作CPU入門6:CPU内部の動き

プログラム・カウンタとバスの状態遷移をアニメで見てみよう

[Webinar/KIT/data]新人技術者のためのRISC-V CPU設計 初めの一歩(5月31日~6月7日,2日コース)

CPUとメモリやI/Oはどうやってデータをやり取りするのか

|

|---|

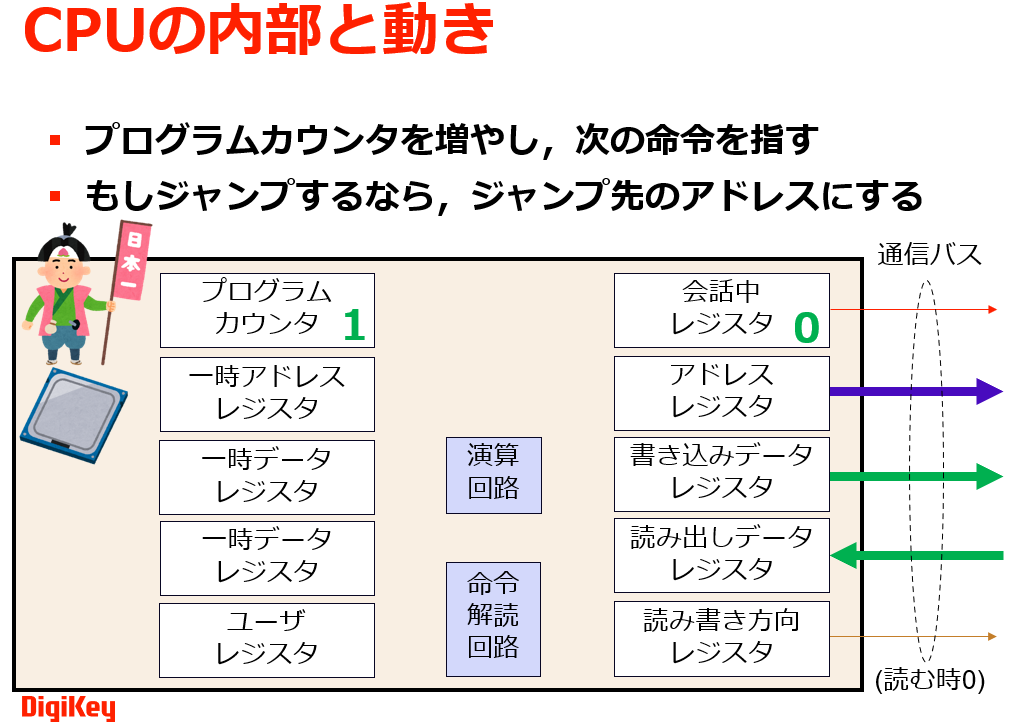

| 図1 CPU設計では,プログラム・カウンタとバス制御信号の適切な実装が安定動作の鍵.各命令の実行ステップを定義し,クロック信号に同期した状態遷移を設計する.画像クリックで動画を見る.または記事を読む |

CPUの内部動作は「命令フェッチ」「ソース取得」「命令実行」「結果書き込み」の4ステップで構成されます.まずプログラム・カウンタ($PC$)が指すメモリ番地から命令を読み出し(フェッチ),解読後に必要なデータをメモリやレジスタから取得します.演算処理後,結果を指定先に書き戻すという流れを繰り返します.

必須のレジスタとその役割

- プログラム・カウンタ($PC$):次に実行する命令のメモリ番地を保持

- アドレス・レジスタ:通信バスに送出するアドレス値を一時保持

- データ・レジスタ:演算前後のデータを一時格納

バス・インターフェースの重要性

CPUは3種類の信号線群で外部と通信します.アドレス・バス(送信先指定),データ・バス(情報転送),制御バス(読み書き方向指示)の組み合わせで,メモリやI/Oデバイスと協調動作を実現します.特に制御バスの「会話中信号」は,バス競合を防ぐ重要な役割を担います.

プログラム・カウンタ($PC$)

命令実行位置を管理する専用レジスタ.各命令実行後,$PC$は自動的にインクリメントされ,次の命令を指します.分岐命令ではジャンプ先アドレスが直接設定されます.

命令フェッチ

$PC$が指すメモリ番地から命令コードを読み出す工程.32ビットや64ビットの命令コードはデコーダで解読され,演算種別や操作対象が決定されます.

バス・アービトレーション

複数デバイスがバスを共有する際のアクセス制御機構.「会話中信号」を使用して,同時通信の衝突を防止します.CPUが信号をアサートすると,ほかのデバイスはバス使用を保留します.

〈著:ZEPマガジン〉

チャプタ・リスト

- 1:09 今回の内容

- 3:23 CPUの中で覚えておくべき情報

- 4:35 CPUの外部インターフェース

- 6:08 CPUの内部の動き

- 13:43 おまけ:自作CPU派に!お勧め開発キット

著者紹介

- NTT,IBM,Sony,NECの各研究所において高性能回路IPやハイレベル・シンセシスの研究,およびプレイステーションなどの製品用SoC開発に従事した後,現職にて民間宇宙ロケットの飛行制御コンピュータの研究開発に従事.FPGAや高位合成を活用している

著書

- [VOD/KIT]一緒に動かそう!Lチカから始めるFPGA開発【基礎編&実践編】,ZEPエンジニアリング株式会社.

- [VOD/KIT]Xilinx製FPGAで始めるHDL回路設計入門,ZEPエンジニアリング株式会社.

- [VOD/KIT]一緒に動かそう!Lチカから始めるFPGA開発【基礎編】,ZEPエンジニアリング株式会社.

- [VOD/KIT]Zynqで初めてのFPGA×Linux I/O搭載カスタムSoC製作,ZEPエンジニアリング株式会社.

- [VOD/KIT]Tiny FPGA実習!高校生から始めるHDLプログラミング,ZEPエンジニアリング株式会社.

- [VOD/Pi KIT]カメラ×ラズパイで一緒に!初めての画像処理プログラミング,ZEPエンジニアリング株式会社.

- スパコンでも破れない!高セキュリティ・マイコン・プログラミング,ZEPエンジニアリング株式会社.

- [YouTube]宇宙軌道ロケット 成功の方程式

- [YouTube]宇宙ロケットの電子回路開発

- FPGA/Zynqで作るカスタム・コンピュータ・チップ,ZEPエンジニアリング株式会社.

- Lチカ入門!ソフトウェア屋のためのHDL事はじめ,ZEPエンジニアリング株式会社.

- USBカメラの動画キャプチャ&描画用 Pythonプログラム,ZEPエンジニアリング株式会社.

- ライブラリ完備!組立式ラズパイI/O増設ボード MCC DAQ HATSファミリ誕生,ZEPエンジニアリング株式会社.

参考文献

- [VOD/KIT] 実習キットで一緒に作る!オープンソースCPU RISC-V入門,ZEPエンジニアリング株式会社.

- [VOD/KIT]ARM Cortex-A9&FPGA内蔵SoC Zynqで初体験!オリジナル・プロセッサ開発入門,ZEPエンジニアリング株式会社.