RISC-V 自作ミニCPUの3段パイプライン命令処理

レジスタ間演算は2段,ロードは3段

レジスタ間演算命令の処理

|

|---|

|

図1 自作したCPUはRV32I命令セットをベースにした超ミニRISC-Vで,3段のパイプラインを採用している.画像クリックで動画を見る.または記事を読む.[著]圓山 宗智 詳細:[VOD]新人技術者のためのRISC-V CPU設計初めの一歩~C言語完全対応!HDLソース500行のミニCPUを一緒に作る~ |

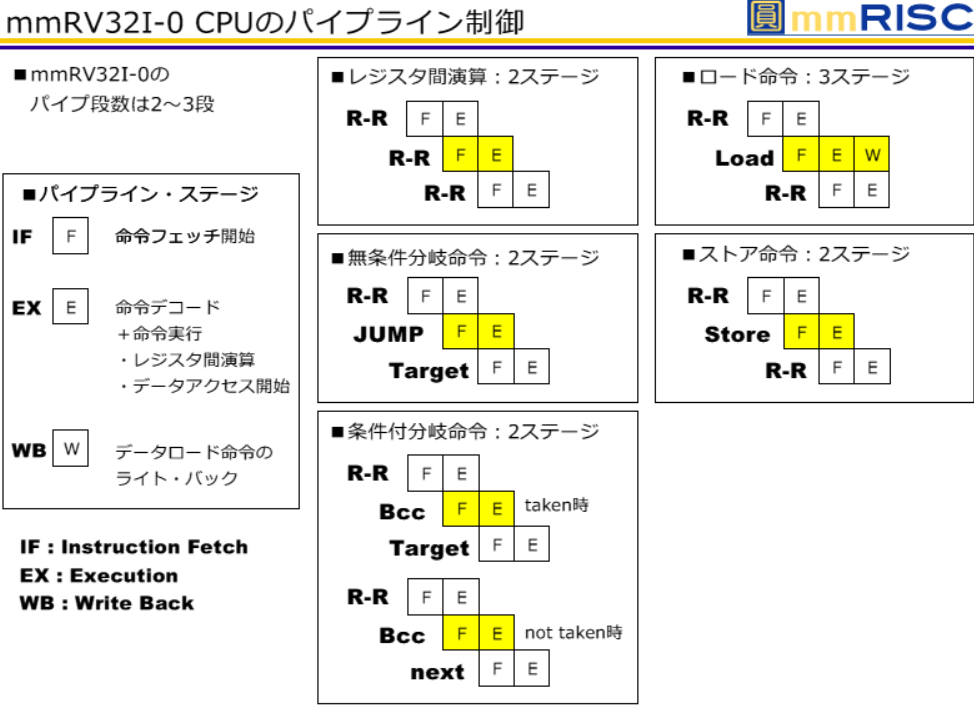

自作したのは,RV32I命令セットをベースにした超ミニRISC-V CPUで,3段のパイプラインを採用しています.パイプラインの各ステージは,命令フェッチ(F),命令デコード+命令実行(EX),データロード命令のライトバック(WB)にわかれています.フェッチ(F)ではプログラム・メモリから命令を読み出し,EXステージで命令をデコードし,レジスタ間演算やデータ・アクセスを開始します.WBステージではロード命令の結果を汎用レジスタに書き戻します.

レジスタ間演算命令の処理

レジスタ間演算命令は2ステージで完了します.EXステージで指定された汎用レジスタ$rs_1$と$rs_2$の値を演算し,その結果を同じステージまたは次クロックでレジスタ$rd$に書き込みます.パイプラインは命令ステージをオーバーラップして処理するため,次の命令も並行してフェッチおよびデコードされます.これにより単純な演算命令でも効率的に処理され,命令間の依存関係がない場合はパフォーマンスが向上します.

ロードおよびストア命令の処理

メモリからデータを読み込むロード命令は3ステージで処理します.EXステージでアクセス先アドレスを計算し,次にメモリからデータを読み出してWBステージでレジスタに書き戻します.ストア命令は2ステージで完了し,EXステージでアドレス計算とライトデータ出力を行い,メモリに書き込む動作を行います.ロード命令の3段パイプラインとストア命令の2段パイプラインを適切に制御することで,パイプラインの効率が維持されます.

分岐命令とパイプライン制御

無条件ジャンプ命令は2ステージで処理し,EXステージでジャンプ先アドレスを計算します.条件付き分岐命令も2ステージで処理され,EXステージでレジスタの比較結果を判定し,分岐成立時はFステージで次の命令フェッチ・アドレスをジャンプ先に挿し換えます.分岐が成立しない場合は次の命令を順次フェッチします.この制御によりパイプラインのステージ間での競合を回避し,命令の連続実行がスムーズに行われます.

- レジスタ間演算命令:F→EXで完了

- ロード命令:F→EX→WBで完了

- ストア命令:F→EXで完了

- 無条件分岐命令:F→EXで完了

- 条件付き分岐命令:F→EXで判定,次ステージで分岐制御

この3段パイプライン構造は,命令フェッチ,デコード+実行,ライトバックを明確に分けることで,レジスタ間演算やロード命令の効率を最適化しています.単純な演算は2ステージで処理され,メモリ・アクセスを伴う命令は3ステージで安全に実行されます.分岐命令におけるターゲット・アドレスの即時計算により,命令フローの乱れを最小化し,CPU全体のパフォーマンスを安定させます.

〈著:ZEPマガジン〉

参考文献

- Lチカ入門!ソフトウェア屋のためのHDL事はじめ,ZEPエンジニアリング株式会社.

- Zynqで作るカスタム・コンピュータ・チップ,ZEPエンジニアリング株式会社.

- [VOD/KIT]一緒に動かそう!Lチカから始めるFPGA開発【基礎編&実践編】,ZEPエンジニアリング株式会社.

- [VOD/KIT]Xilinx製FPGAで始めるHDL回路設計入門,ZEPエンジニアリング株式会社.

- [VOD/KIT]Zynqで初めてのFPGA×Linux I/O搭載カスタムSoC製作,ZEPエンジニアリング株式会社.

- [VOD]カメラ×ラズパイで一緒に!初めての画像処理プログラミング

- [VOD/KIT] 実習キットで一緒に作る!オープンソースCPU RISC-V入門,ZEPエンジニアリング株式会社.

- [VOD/KIT]ARM Cortex-A9&FPGA内蔵SoC Zynqで初体験!オリジナル・プロセッサ開発入門,ZEPエンジニアリング株式会社.