PLLシンセの安定性設計:ループ・ゲインのカットオフ調整

発振余裕/ノイズ/周波数ロックアップ時間を最適化

|

|---|

|

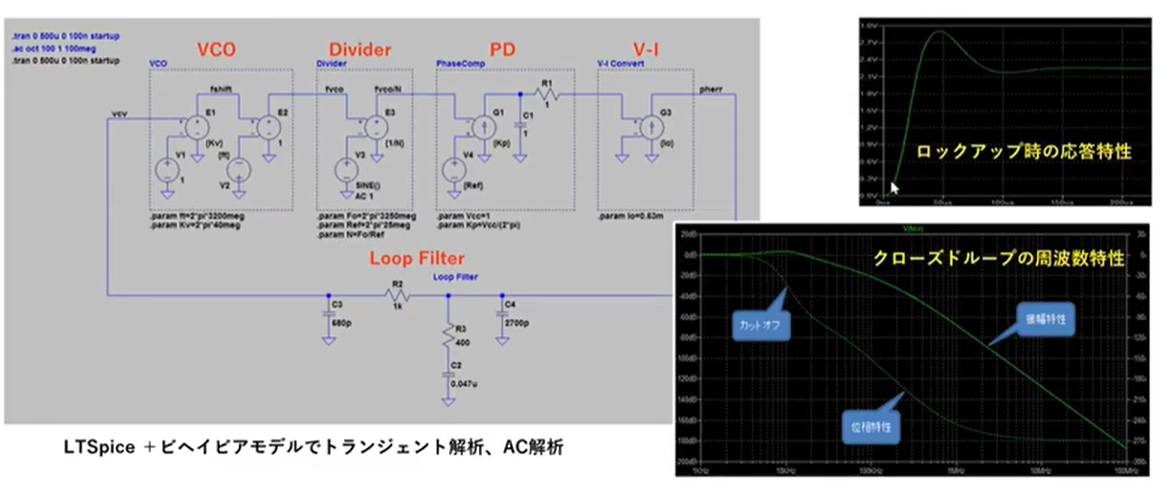

トランジェントにおけるロック収束の過程や,クローズドループの周波特性,フィードバック回路の重要性,ノイズ対策について解説し,安定した応答特性を得るための工夫を述べる 画像クリックで動画を見る.または記事を読む [著]加藤 隆志 詳細:[VOD/KIT]GPSクロック・ジッタ・クリーナ |

PLLシンセのループ・ゲインカットオフ調整の重要性

PLL(位相同期ループ)シンセサイザの安定性を確保するためには,ループ・ゲインのカットオフ周波数を適切に設定することが欠かせません.カットオフ周波数は,システムの周波数ロックアップ時間や発振余裕に大きく影響します.ロックアップ時間は,PLLが初期状態から目標周波数に同期するまでの時間であり,一般的に数百μs程度が目安です.この時間が長すぎると応答が遅くなり,短すぎるとシステムの安定性が損なわれる可能性があります.

周波数特性を観察すると,ループ・フィルタの設計が安定動作に直結していることがわかります.ループ・フィルタは,フェーズ・ディテクターからのノイズを低減し,VCO(電圧制御発振器)に伝わる不要な変動を抑制する役割を担います.フェーズ・ディテクターの出力はパルス状のノイズ成分を含むため,このノイズを適切にフィルタリングしなければVCOの周波数が乱され,出力信号の品質が低下します.

発振余裕とノイズ低減のためのループ・フィルタ設計

ループ・フィルタは1次フィルタで基本的なノイズ除去を行いますが,2次・3次フィルタを用いてさらに高周波領域のノイズを抑制することが可能です.これにより,位相の遅れを追加しつつ,発振のリスクを低減させる効果があります.ただし,カットオフ周波数付近で位相が過度に回るとループ内での発振が発生しやすくなります.したがって,この周波数帯域の位相回転を最小限に抑える工夫が求められます.

適切に設計されたループ・フィルタは,位相の回転を制御しつつ,ノイズを十分に減衰させることで安定した応答を実現します.これにより,PLLシンセのロックアップ時にリンギング(過渡応答の振動)が早期に収束し,発振せずに安定動作が可能になります.逆にリンギングが長時間続いたり,振幅が増大する場合はループ設計に問題があると判断できます.

ロックアップ時間の最適化とシステム安定性の評価

ロックアップ時間はループ・ゲインのカットオフ周波数の設定により決まります.カットオフ周波数を高く設定するとロックアップ時間は短縮されますが,システムの発振余裕が減少しノイズの影響も大きくなりやすいです.逆に低く設定すると安定性は向上しますが,ロックアップに時間がかかってしまいます.設計段階ではこれらのトレードオフを考慮し,最適なカットオフ周波数を選定する必要があります.

ロックアップ時の過渡応答を観察することでシステムの安定性を評価できます.安定したPLLシンセはリンギングが速やかに収束し,発振が生じません.不安定な場合はリンギングが収まらず,振幅が増加する傾向が見られます.このような特性をモニタリングしながらループ・フィルタのパラメータを調整することが,安定かつ高速なロックアップを実現するうえで重要です.

- ループ・ゲインのカットオフ周波数設定はロックアップ時間と発振余裕に影響する

- ループ・フィルタはノイズ低減と位相回転の制御を両立させる必要がある

- 過渡応答の観察でPLLの安定性を評価し最適設計に反映させる

参考文献

- [VOD]MATLAB/Simulink×FPGAで作るUSBスペクトラム・アナライザ,ZEPエンジニアリング.

- [VOD/KIT]3GHzネットアナ付き!RF回路シミュレーション&設計・測定入門,ZEPエンジニアリング.

- [VOD/KIT]3GHzネットアナ付き!初めてのIoT向け基板アンテナ設計,ZEPエンジニアリング.

- [VOD/KIT]初めてのソフトウェア無線&信号処理プログラミング 基礎編/応用編,ZEPエンジニアリング.

- [VOD]Pythonで学ぶ マクスウェル方程式 【電場編】+【磁場編】,ZEPエンジニアリング.