Access:376

ZEPマガジン

|

2025年5月16日号 [ロボット/自動運転/宇宙]

GPS衛星が出す電波 GPS衛星NAVSTARは,10.23MHzを基準とした複数の周波数で電波を送信し,民生用と軍用に対応した測位信号を提供している |

|

2025年5月15日号 [ロボット/自動運転/宇宙]

衛星測位の原理は三角測量 GNSS測位は三角測量を基礎に,電波の伝搬時間や搬送波位相の解析により高精度な位置と方位を求める技術 |

|

2025年5月14日号 [ロボット/自動運転/宇宙]

GNSSコンパスによる飛行機の姿勢角推定 ピッチ角,ロール角,ヨー角といった姿勢情報のうち,ヨー角は慣性センサでは精度確保が難しいため,GNSSによる推定が有効 |

|

2025年5月13日号 [FPGA/HDL/論理回路]

[AI/IoT/マイコン]

Xyloniボード上の全リソースを活用するプログラム Xyloniボードに搭載されたプッシュ・ボタン,LED,SDカード・スロットの全機能を利用するプログラムXyloni_BoardTestを制作 |

|

2025年5月12日号 [FPGA/HDL/論理回路]

[AI/IoT/マイコン]

コンピュータ対戦型Tic-Tac-Toeゲームの作成 Tic-Tac-Toeゲームは3×3のマスで行う二人零和有限確定完全情報ゲーム.すべての手がオープンに共有される構造で,アルゴリズムの実装と検証に非常に適する |

|

2025年5月11日号 [FPGA/HDL/論理回路]

[AI/IoT/マイコン]

超小型XyloniボードにRISC-V Sapphire SoCを実装する Interface Designerは,FPGA内の周辺機能と物理端子との橋渡しを行うツール.Efinityにおいて,論理設計と物理設計を明確に分離するという設計思想を反映している |

|

2025年5月10日号 [FPGA/HDL/論理回路]

[AI/IoT/マイコン]

超小型Xyloniボードで動かすRISC-V Sapphire SoC Xyloniは,USBコネクタ,ユーザ用ボタン,LED,SDカード・スロットといった実用的なI/Oを搭載.制御信号はTrion T8 FPGAに直結しており,ユーザ・ロジックから自由に制御できる |

|

2025年5月9日号 [FPGA/HDL/論理回路]

[AI/IoT/マイコン]

Efinix社のRISC-V IPコア Sapphire SoC Sapphire SoCは,RISC-Vアーキテクチャをベースとした32ビットCPUコアと多様な周辺機能を組み合わせたIPコア.VexRiscvをコアに据え,パイプライン処理や割込み対応,例外処理などを網羅 |

|

2025年5月8日号 [FPGA/HDL/論理回路]

[AI/IoT/マイコン]

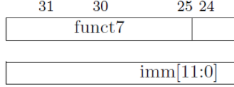

オープンソースな命令セットRISC-V RISC-Vは自由に扱えるISA.FPGAとの組み合わせにより,アーキテクチャを自分で設計し,学ぶことができる |

|

2025年5月7日号 [FPGA/HDL/論理回路]

[AI/IoT/マイコン]

Efinix社のFPGA Efinix社のTrion FPGAは,安価ながらも高い柔軟性をもち,RISC-Vプロセッサの実装も可能.40nmプロセスのTrionシリーズは,I$^$2CやSPIに加えて,DDRやLVDSにも対応する |

|

2025年5月6日号 [AI/IoT/マイコン]

[信号処理/セキュリティ]

音を目で見る!オーディオ・スペクトログラムの制作 マイクから拾った音のスペクトログラムをLCDに表示するプログラムを実装し,人間には聞こえない音を目で見る.音声や振動など,時間とともに変化する周波数成分を分析できる |

|

2025年5月5日号 [FPGA/HDL/論理回路]

[AI/IoT/マイコン]

自作CPU入門8:プログラミングしやすい回路作り CPUを自作するならプログラムを効率的に動かすために,割り込み処理やパイプライン,スタックなどを導入したい |

|

2025年5月4日号 [AI/IoT/マイコン]

[信号処理/セキュリティ]

スピーカ周波数特性テスタの実装 STM32H747I-DISCOとTouchGFXを組み合わせることで、GUI付きのオーディオ分析ツールを制作.周波数スイープとスペクトル表示を組み合わせれば、手軽にスピーカの特性を可視化できる |

|

2025年5月3日号 [FPGA/HDL/論理回路]

[AI/IoT/マイコン]

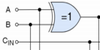

自作CPU入門7:CPU内部の回路 CPU内部のレジスタは,フリップフロップという回路素子で作る.レジスタの間の通信経路はセレクタという回路素子を組み合わせて作る.計算回路は加算回路を組み合わて作る |

|

2025年5月2日号 [FPGA/HDL/論理回路]

[AI/IoT/マイコン]

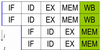

自作CPU入門6:CPU内部の動き プログラム・カウンタとバス制御信号の適切な実装がCPUの安定動作の鍵.各命令の実行ステップを定義し,クロック信号に同期した状態遷移を設計する |

人気のZEPマガジン

ZEPマガジン総アクセス数: 294,168

- ラズベリー・パイ Picoマイコン入門 C言語開発環境の構築 (54,012 views)

- Pythonではじめる 数値解析入門 (19,705 views)

- 無帰還純A級オールディスクリート・ヘッドホン・パワーアンプの製作 (12,663 views)

- 最新研究 Raspberry Pi 4のGPUプログラミング (7,703 views)

- GNU Radio×USRPで作るソフトウェア無線機 (6,739 views)

- スペアナ入門 RBWとVBW (5,105 views)

- OPアンプ増幅回路の2つのゲイン (4,519 views)

- 高感度受信!ソフトウェア無線機の心臓部“Root-Raised Cosine Filter”の設計 (3,913 views)

- 故障推定から画像認識まで!「主成分分析」による最高性能AIエッジ開発 (3,811 views)

- 大規模言語モデルLLM入門 その3 モデルの簡易化「蒸留」 (3,311 views)