RF用PLLのVCOには超低雑音LDO

100k~700MHz,精度-10乗!GPSクロック・ジッタ・クリーナ

|

|---|

| ウルトラ・ロー・ノイズ電源の評価基板では,アナログデバイスの高性能部品を使用し,特にPSRR特性が優れていることが強調され,選択肢が増えたことの利便性が述べられている 〈著:加藤 隆志〉 |

| 【出典】:[VOD/KIT]GPSクロック・ジッタ・クリーナ |

| 画像クリックで動画を見る.または記事を読む |

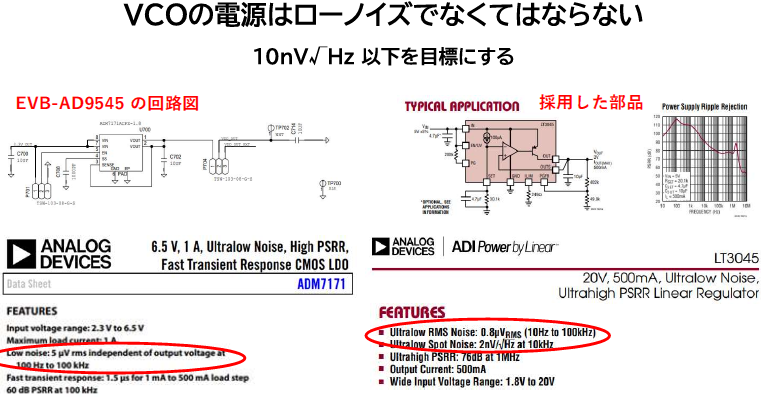

PLLのVCOに求められる超低雑音LDOの重要性

位相同期ループ(PLL)の電圧制御発振器(VCO)には,極めて低いノイズ特性をもつ電源供給が不可欠です.VCOの電源にノイズが混入すると,出力信号の位相ノイズやジッタが増加し,システム全体の性能を著しく損ないます.特にGPSクロックや通信機器のジッタ・クリーナ用途では,100kHz以下のノイズ成分が重要視されます.

従来の汎用LDO(低ドロップアウト・レギュレータ)では,ノイズ性能が十分でないためVCO電源には適しません.ノイズ密度が10nV/$\sqrt{\text{Hz}}$以下,かつ100Hzから100kHzの帯域で積分したノイズ電圧が5$\,\mu\mathrm{V}$以下であることが望ましい基準です.このレベルのノイズ低減が実現できるLDOを採用することが,VCOの高性能化に直結します.

超低雑音LDOの特性と選定基準

超低雑音LDOは,電源ラインに乗るリプルや高周波ノイズを効果的に抑制する性能をもちます.代表例としてアナログ・デバイセズの製品が挙げられます.このLDOの特筆すべき点は,100Hzから100kHzの周波数帯におけるノイズを積分した総合ノイズ電圧が5$\,\mu\mathrm{V}$以下であることです.ノイズ密度で換算すると約17nV/$\sqrt{\text{Hz}}$となり,VCOの要求レベルを大幅に上回ります.

また,PSRR(電源変動除去率)が高く,電源のリプルをほぼ通さない特性も重要です.評価基板(EVB)で実際に使用されている回路例では,10kΩの抵抗と$1\,\mu\mathrm{F}$のキャパシタによるリプル・フィルタを組み合わせることで,さらにノイズ低減効果を高めています.

実装上の注意点と周辺配慮

超低雑音LDOを用いたVCO電源回路では,ノイズ源となるディジタル信号線からの干渉を避けるため,基板設計も重要です.内層にディジタル配線を通す場合は,電源線から十分に距離を取ることが推奨されます.電源ラインのインピーダンスを低く保ち,安定した電圧供給を確保するために,適切なデカップリング・キャパシタの配置も欠かせません.

近年は,トランジスタで自作していた超低ノイズ電源回路が,市販の高性能LDOに置き換わり,設計の手間が大幅に軽減されています.7V程度の出力電圧をもつ製品が多く,さまざまなシステムに容易に適用可能です.これにより高精度GPSクロックやジッタ・クリーナの性能向上が期待できる環境が整っています.

- PLLのVCO電源にはノイズ密度10nV/$\sqrt{ \text{Hz}}$以下のLDOを選ぶ

- 100Hz$\sim$100kHz積分ノイズ電圧は5$\,\mu\mathrm{V}$以下が目安

- リプル・フィルタを組み合わせてさらなるノイズ低減を図る

- 基板設計でディジタル線路からの干渉を避ける

- 市販の高性能LDOの利用で設計工数を削減可能

参考文献

- Arm M4/M7/DSP×500MHz!STM32H7ハイスペック計測通信Module開発,ZEPエンジニアリング株式会社.

- 高感度受信!ソフトウェア無線機の心臓部“Root-Raised Cosine Filter”の設計,ZEPエンジニアリング株式会社.

- [VOD]MATLAB/Simulink×FPGAで作るUSBスペクトラム・アナライザ,ZEPエンジニアリング株式会社.

- [VOD/KIT]初めてのソフトウェア無線&信号処理プログラミング 基礎編/応用編,ZEPエンジニアリング株式会社.

- [VOD]Pythonで学ぶ マクスウェル方程式 【電場編】+【磁場編】,ZEPエンジニアリング株式会社.

- 実験しながら学ぶフーリエ解析とディジタル信号処理[Vol.1:フーリエ解析の基本「三角関数」の正しい理解]

- [VOD]Pythonで学ぶ やりなおし数学塾2【フーリエ解析】

- [VOD/KIT]STM32マイコン&Wi-Fiモジュールで学ぶ C/C++プログラミング入門,ZEPエンジニアリング株式会社.

« ZEPマガジン前の記事「16ピンDIP FPGAでLチカ」