HDL入門:IPコアの登録と接続

Lチカから始めるFPGA開発 超入門

|

|---|

|

プロジェクトにIPコアが登録され,次のステップとして自分のデザインに組み込む作業を行うことを説明している 〈著:森岡 澄夫〉 出典:[VOD/KIT]一緒に動かそう!Lチカから始めるFPGA開発【基礎編&実践編】

画像クリックで動画を見る.または記事を読む |

HDLにおけるIPコアの登録と設計への組み込み

FPGA開発の初歩として,IPコアの登録と接続は重要なステップです.IPコアとは,あらかじめ設計された回路ブロックのことで,再利用性が高く設計効率を向上させる役割を担います.IPコアをプロジェクトに登録すると,ツール上で利用可能な状態になります.登録が完了したか不安な場合は,用意されたサンプル・プロジェクトを開いて動作を確認する方法が有効です.

登録したIPコアを自分の設計に組み込む場合,VerilogやVHDLのコード中でインスタンス化を行います.これを「インスタンシエーション」と呼びます.作成したIPコアは単なるブラックボックスとして扱われるため,接続端子を正しく指定しなければなりません.複数の同一IPコアを使う場合は,各々に固有のインスタンス名やIDを割り当てて区別します.

IPコア接続時のコード記述のポイント

IPコアを接続する際のコードは決まった書式に従います.まず,モジュール名として自分が作成したIPコアの名前を指定します.続いてインスタンス名を付けることで,同じIPコアを複数使う場合にも識別可能にします.端子の接続は,ワイアーやレジスタを介して自分の設計内の信号と対応させます.

例えば,クロックやリセット信号は外部からの入力としてIPコアに接続します.これらの信号は設計全体の同期や初期化に不可欠です.クロック信号はFPGA内のメインクロックと一致させる必要があります.リセット信号は設計の安定動作を保証するため,明確に接続することが望ましいです.

インスタンス化したIPコアの端子に対しては,設計内の該当信号をつなぎます.クロック,リセット,データ入出力などの各信号を対応させることで,IPコアが設計内で正しく動作します.特に複数のIPコアを使う場合は,各IPコアの端子接続に誤りがないか慎重に確認することが必要です.

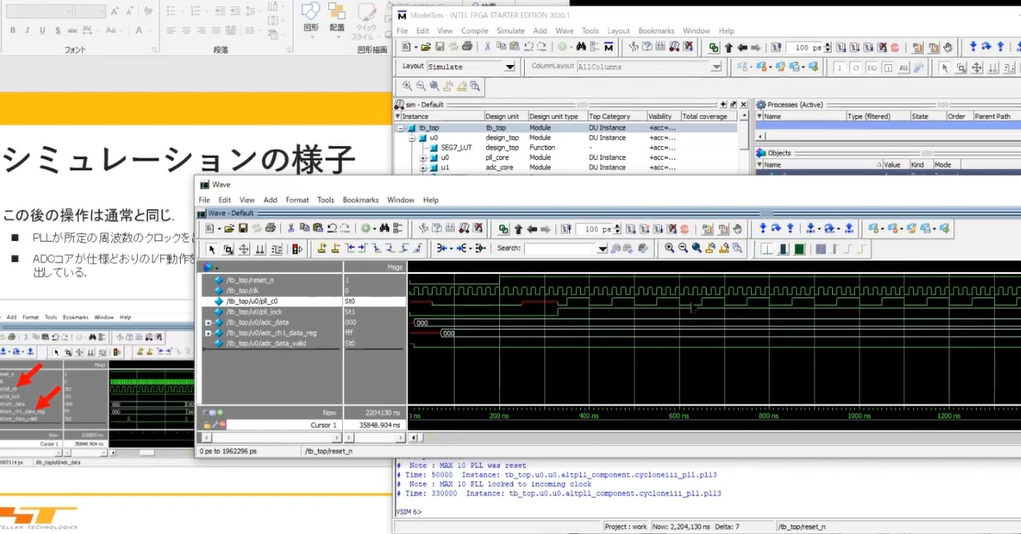

設計の検証とサンプル・コードの活用

IPコアを組み込んだ設計は,まずシミュレーションやベリログコードの確認を行います.サンプル・コードにはコメントが付けられていることが多く,IPコアの接続方法や信号の役割が理解しやすくなっています.設計が正しく動作しているか不安な場合は,用意されたサンプル・プロジェクトを参考にしながら進めるとよいです.

FPGA開発では,クロックやリセットの信号接続ミスがトラブルの原因になることが多いです.設計段階でこれらの信号が正しくIPコアに接続されているか確認します.IPコアの動作確認ができたら,LEDへの出力やスイッチ入力の制御など具体的な機能実装へ進みます.こうした段階的な検証が開発の効率化につながります.

- IPコアをプロジェクトに登録し利用可能な状態にする

- 自分の設計内でIPコアをインスタンス化し端子を接続する

- クロックやリセット信号の接続を正確に行う

- サンプル・コードを参考にしながら設計の動作確認を行う

- 動作確認後に具体的な制御機能の実装へ進む

参考文献

- [VOD/KIT]Xilinx製FPGAで始めるHDL回路設計入門,ZEPエンジニアリング株式会社.

- [VOD/KIT]実習キットで一緒に作る!オープンソースCPU RISC-V入門,ZEPエンジニアリング株式会社.

- [VOD/KIT/data]新人技術者のためのRISC-V CPU設計 初めの一歩,ZEPエンジニアリング株式会社.

- [VOD/KIT]Zynqで初めてのFPGA×Linux I/O搭載カスタムSoC製作,ZEPエンジニアリング株式会社.

- [VOD/KIT]Zynqで初めてのFPGA×Linux I/O搭載カスタムSoC製作,ZEPエンジニアリング株式会社.

- [VOD/KIT]強度128ビット! AES暗号セキュリティ・プログラミング入門,ZEPエンジニアリング株式会社.

- [VOD/KIT]カメラ×ラズパイで一緒に!初めての画像処理プログラミング ,ZEPエンジニアリング株式会社.

« ZEPマガジン前の記事「実験しながら学ぶフーリエ解析とディジタル信号処理[Vol.1 フーリエ解析の基本「三角関数」の正しい理解]」

ZEPマガジン次の記事「高周波対応シミュレータ Qucsで学ぶアナログ電子回路 超入門[第1回 プリント・パターンは$L$と$C$でできている]」 »