計測のための24ビット$\Sigma\Delta$型A-Dコンバータ活用[第2回 実験研究!市販ICの内蔵ノイズ・シェーピング回路]

雑音を高周波に集めてLPFできれいに取り除く

【Index】

計測用途で注目される24ビット$\Sigma\Delta$(シグマ・デルタ)A-Dコンバータは,高分解能かつ高い信号対ノイズ比($SNR$)を実現できるICです,本記事は特に,アナログ・デバイセズ社の絶縁型$\Sigma\Delta$変調器AD7401を用いて,内蔵ノイズ・シェーピングの実験的検証を行った内容を解説します.読者対象は,電子回路設計者や計測エンジニア,ADCの動作原理に興味をもつ技術者,大学・大学院の学生などです.

$\Sigma\Delta$型ADCは,1ビットのADCにより入力信号電圧を高速サンプリングしてシリアル・データ出力を得て,それを入力にフィードバックすることにより量子化ノイズを高周波側に押しやるノイズ・シェーピング技術を用いています.今回の実験的検証の実際のシリアル・データ波形やスペクトル解析から,入力信号電圧成分とノイズ・シェーピングされた量子化ノイズの分布が確認でき,これが高い分解能の理由なのだと納得できます.

また,実際の$\Sigma\Delta$型ADCではこの1ビット・データを多数回平均化するディジタルLPF処理が行われており,これが$SNR$向上に寄与します.平均化フィルタはsinc関数形状の伝達特性をもち,複数段を連結することで減衰特性を強化でき,より狭帯域での高精度計測を可能にしています.さらに,$\Sigma\Delta$変調器の次数を上げることでノイズ・シェーピングの効果が高まり,より優れた性能を実現します.

最近では,こうした16~32ビットの$\Sigma\Delta$ ADCが高精度な音響機器や医療機器,工業用センサなど幅広い分野で応用されており,ノイズ・シェーピング技術の理解はシステム設計の要(かなめ)となっています.ただし,量子化ノイズに対して有効なノイズ・シェーピングは,ADC入力段の物理的な回路ノイズには効果がない点に注意が必要です.〈著:ZEPマガジン〉

1.はじめに

第1回は,高分解能を可能にするA-D(Analog-to-Digital)コンバータ(本稿では以降「ADC」と呼ぶ)である, (シグマ・デルタ)型ADCの「ノイズ・シェーピング技術」について,数式的にそのしくみを説明してきました.A-D変換で生じる量子化誤差電圧(量子化ノイズ)のエネルギを「高い周波数に押しやる」という動作は,量子化ノイズが時間微分したかたちで出力に現れるからだと説明しました.

今回は$\Sigma\Delta$型ADCの初段部分,「$\Sigma\Delta$変調器」の部分だけが用意されている,アナログ・デバイセズの絶縁型$\Sigma\Delta$変調器AD7401を用いてノイズ・シェーピングのようすを実測してみます.実測により,$\Sigma\Delta$型ADCが1ビット・データ出力(シリアル・ビット列)で動作しているにもかかわらず,なぜ高い分解能と$SNR$(Signal to Noise Ratio; 信号対ノイズ比)が実現できるのかさらに納得できるでしょう.

なおこの方式を「ΔΣ方式」と呼ぶ場合もありますが,アナログ・デバイセズでは「$\Sigma\Delta$方式」と呼んでいます.実際はどちらも同じものです.

2.$\Sigma\Delta$変調器の実際のノイズ・シェーピングを観測してみる基板

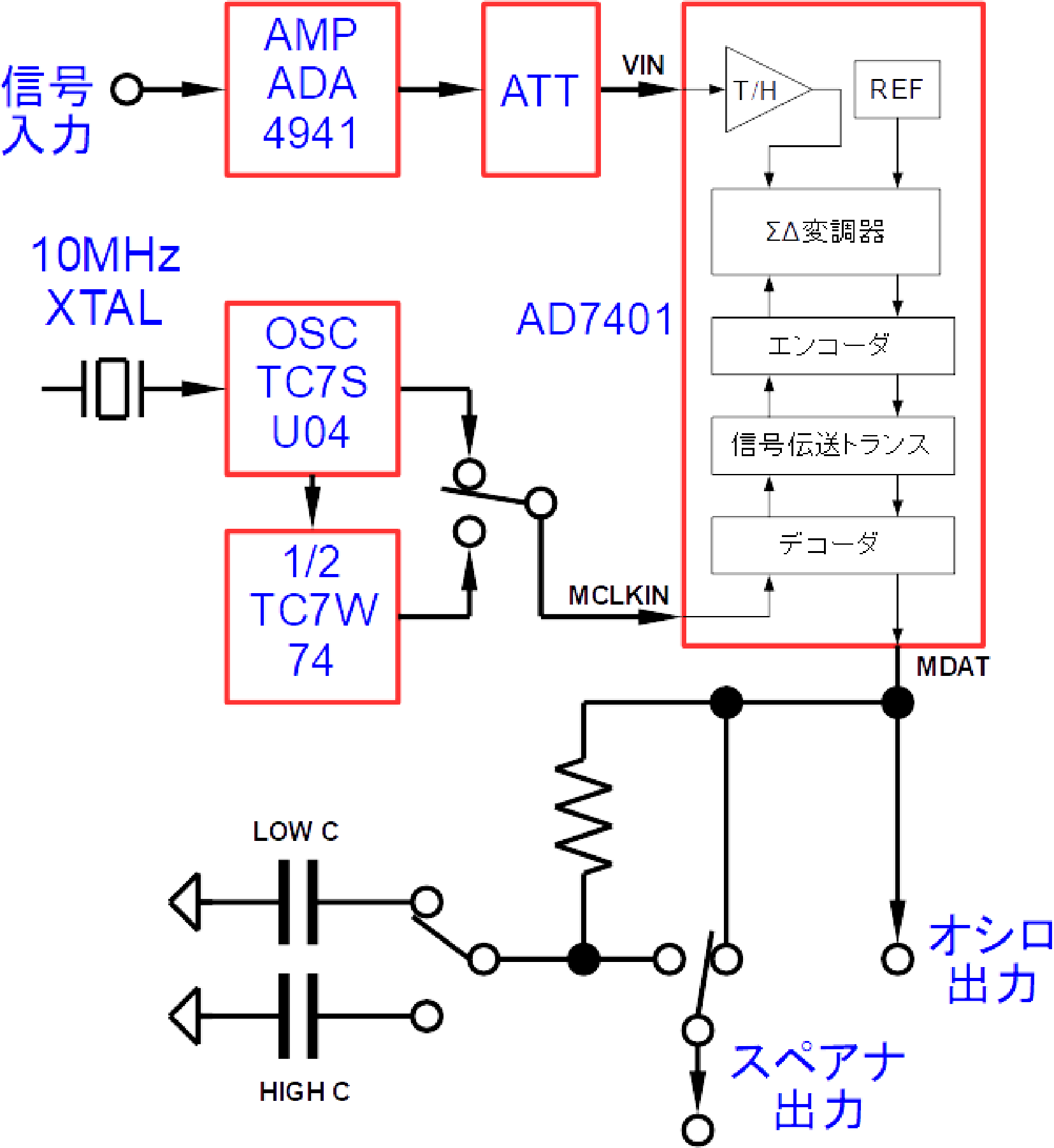

図1は,私が製作した絶縁型$\Sigma\Delta$変調器AD7401(アナログ・デバイセズ製)によるノイズ・シェーピング特性を観測できる基板のブロック図です.AD7401自体の内部ブロックも示しています.

AD7401は$\Sigma\Delta$変調器側とA-D変換出力側(これまで出力$Y$と示してきたもの)は,「ディジタル・アイソレータ」というもので直流的に分離されています.このディジタル・アイソレータについては本稿の議論の対象外なので,興味あるかたは稿末の参考文献[1]などを参照してください.なおこの基板では同じグラウンド電位となるように,グラウンド端子を相互に接続しています.

この基板ではノイズ・シェーピング動作を目視するため,$\Sigma\Delta$変調器出力(MDAT出力.前回「出力$Y$」と説明してきたもの)を,ディジタル・フィルタによるLPF(Low Pass Filter)処理を行わず,キャパシタと抵抗による$RC$アナログ1次LPFでフィルタリングをするという方法をとっています.これにより$\Sigma\Delta$変調器によるノイズ・シェーピングと,それをフィルタリングして$SNR$を向上させるふるまいを目視で確認できます.

3.実際に波形を見てみる

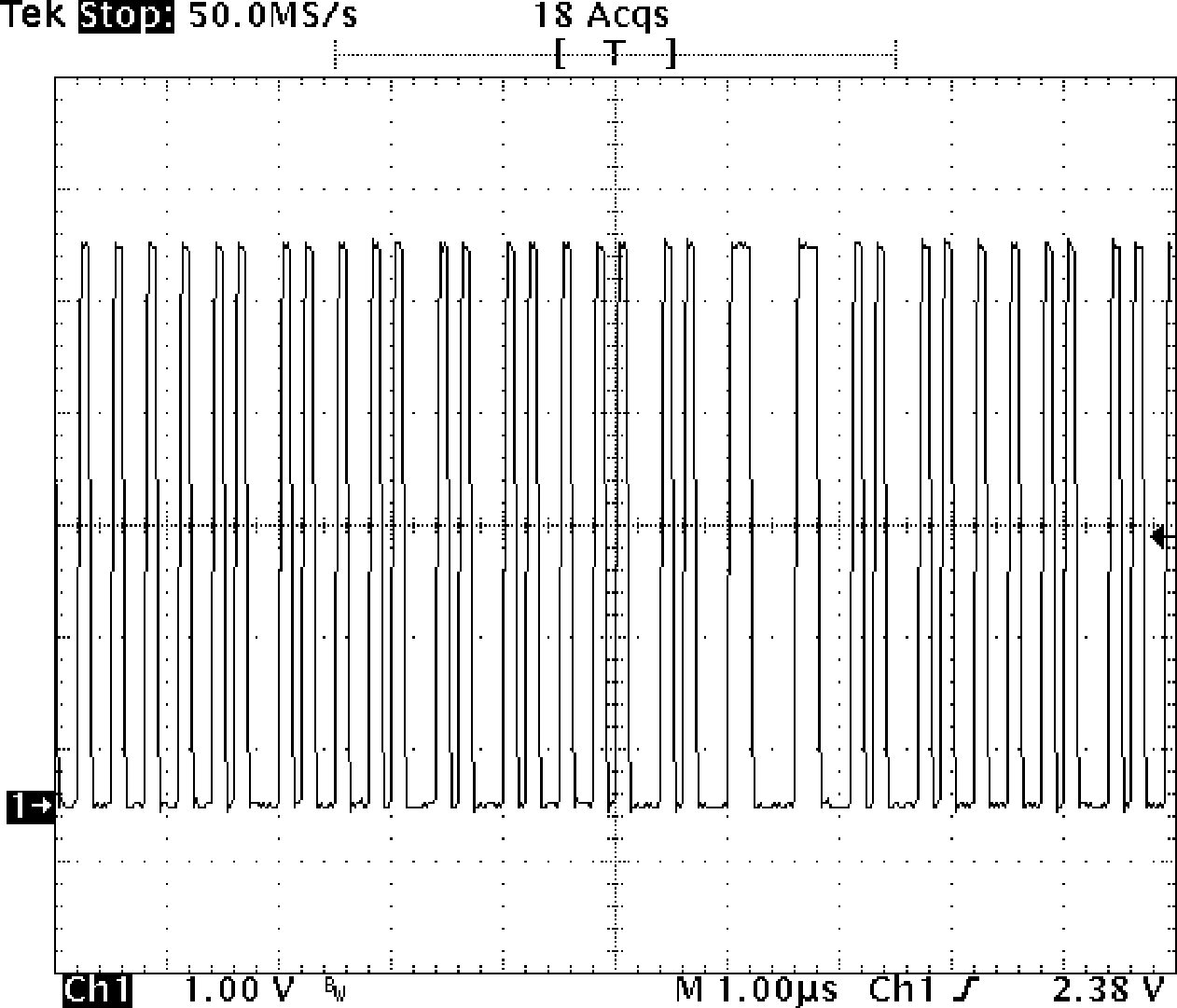

図2はAD7401のMDAT出力(1ビット・データ出力)をそのままオシロスコープで観測したようすです.

サンプリング・クロック(動作クロックMCLK)は10 MHzです.基板への入力電圧は1 Vで,それが入力部の抵抗で分圧され,AD7401の入力端子VIN+, VIN-の端子間電圧は+100 mVになっています.出力波形は同図のように,ランダム的なH/Lになっており,何ら情報をもっていないように見えます.これは第1回に示したように,$\Sigma\Delta$変調器での1回のサンプリングで得られた1ビット・データ(MDAT出力)はほとんど意味を持たないからです.

実際にノイズ・シェーピングされたスペクトルを見てみる

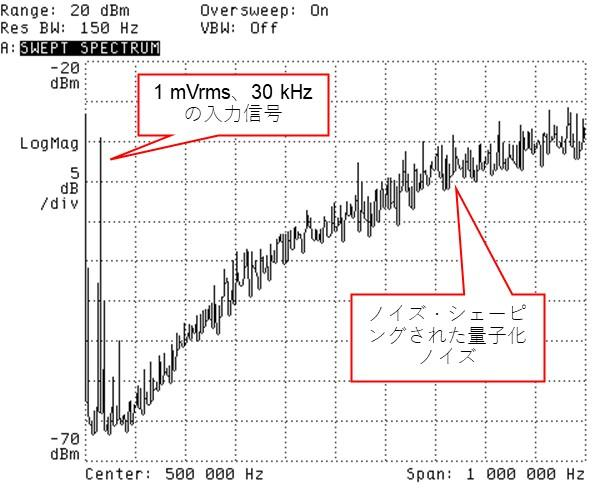

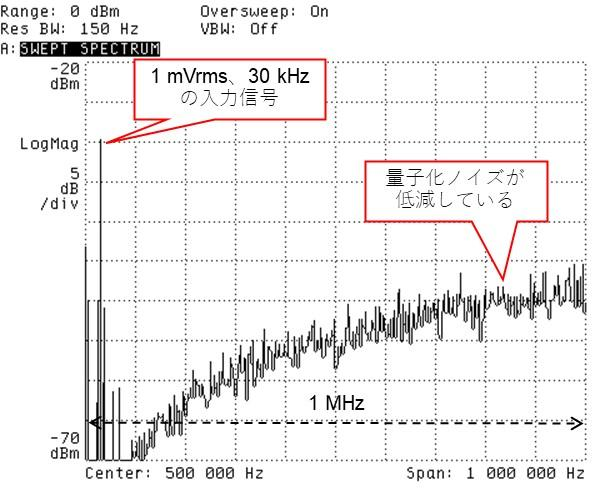

続いて入力電圧を1 mV$_\mathrm{RMS}$(フル・スケールの$-$43 dB),30 kHzの交流電圧にして,スペクトラム・アナライザでMDAT出力を観測したようすを図3に示します.

観測帯域は1 MHzです.さきのオシロスコープによる時間軸波形では,何ら情報をもっていないように見えましたが,スペクトラムを観測してみると,加えた交流電圧の成分が30 kHzのところに立っており,また量子化ノイズが高域周波数に押しやられ,整形つまりノイズ・シェーピングされていることがわかります.「なるほど,納得」ですね.

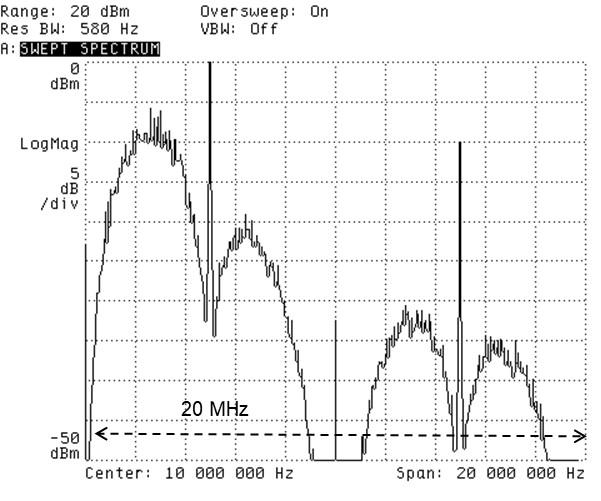

スペクトラム・アナライザの観測帯域をサンプリング・クロック(MCLK)周波数10 MHzの倍の20 MHzまで広げてみると(図4),ディジタル信号処理の教科書で見る,「5 MHzを中心とした対称の折り返し」になっていません.5 MHzを越えていくあたりからスペクトルのレベルが低下しています.ディジタル信号処理理論やここまでの数式による理論検討と少しの差異があることに気がつきます.

この理由は,ディジタル信号処理理論の視点では信号を「インパルス」(幅がなく,大きさが1のパルス)として取り扱う一方,AD7401の出力は1サンプルあたり0.1 $\mu$secの台形波である,という違いによるものです.この台形波形状を「ゼロ次ホールド」といい,稿末の参考文献[2]や[3]に説明があります.

LPFでノイズ・シェーピングされたスペクトルを取り去る

続いて,基板上に用意してある1次の$RC$アナログLPFをオンして,$-$3 dBカットオフ周波数100 kHzの設定でMDAT出力スペクトルを観測してみます.結果を図5に示します.高域周波数に存在していたノイズ・シェーピングされた量子化ノイズがLPFのフィルタリングにより低減し(1次LPFなので高域のノイズ低減度は限定的だが),$SNR$が大きく向上しており,分解能を高められるようすがわかります.これが$\Sigma\Delta$型ADCの動きなのです.

実際の$\Sigma\Delta$型ADCでは,$\Sigma\Delta$変調器からの1ビット・データのシリアル・ビット列をビット拡張しディジタルLPFで処理しますが,その基本動作は図5のアナログLPFとまったく変わりません.このノイズ・シェーピング特性観測基板で,ディジタルLPF処理のようすも目視で確認(体感)できるというわけです.

|

|---|

| 図5 ノイズ・シェーピングされた量子化ノイズを$RC$アナログLPFでフィルタリングすれば$SNR$が向上する(これが$\Sigma\Delta$ 型ADCの動き.1次LPFなので高域のノイズ低減度は限定的) |

4.実際の$\Sigma\Delta$型ADCでも原理は同じ

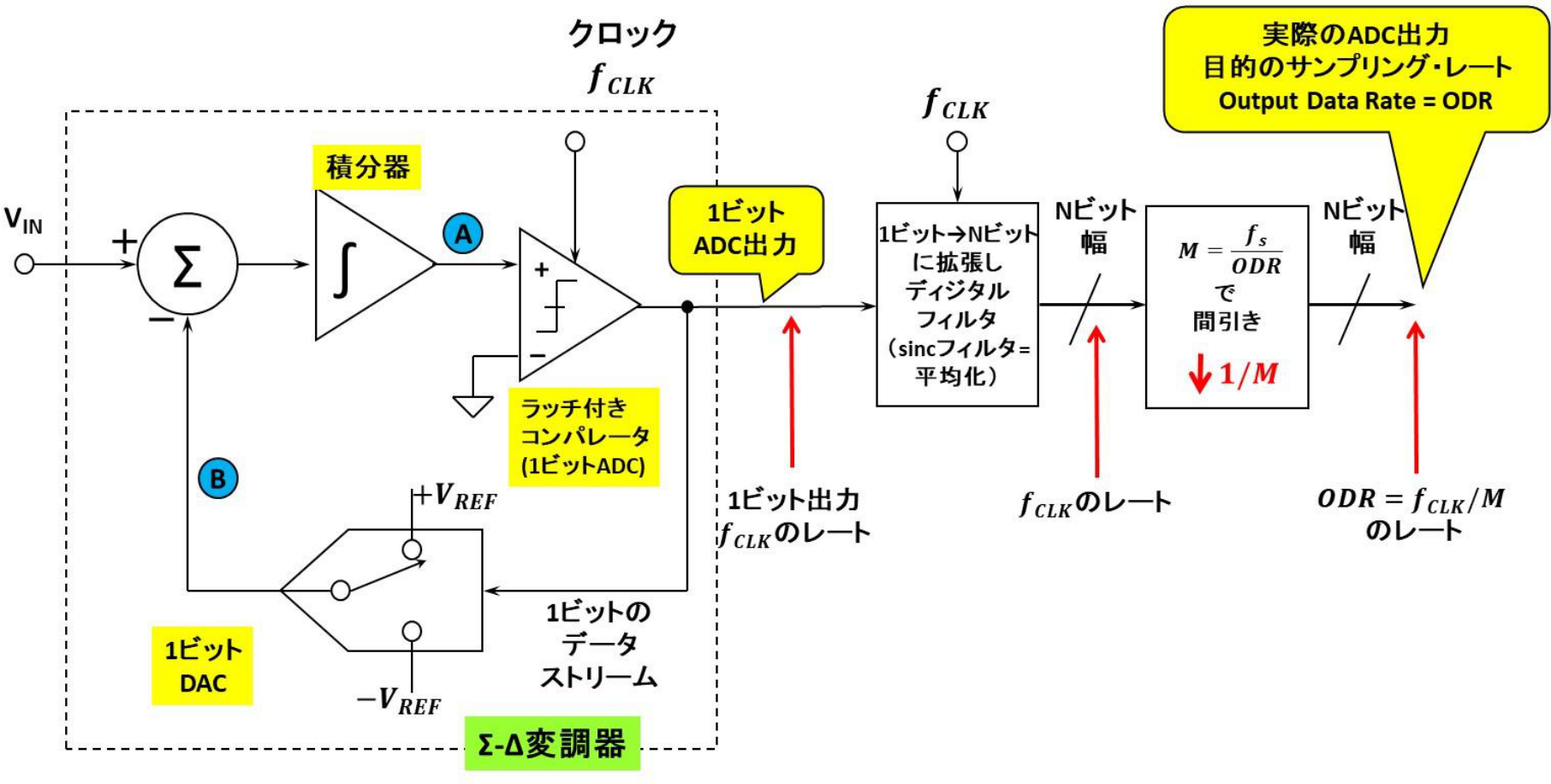

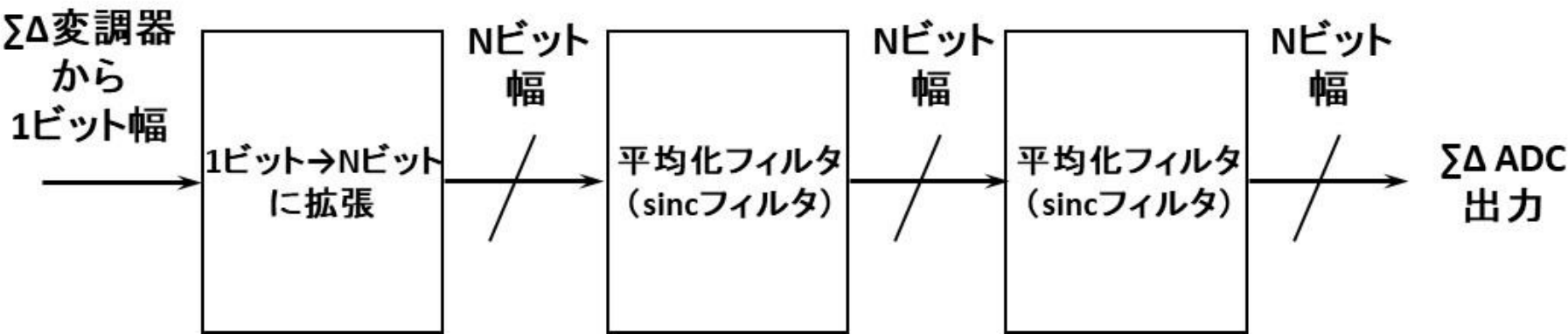

ここまで示してきた$\Sigma\Delta$変調器は,実際の$\Sigma\Delta$型ADCの初段を構成するものであり,基板後段のアナログLPFは平均化フィルタとしてディジタル回路で構成されます(図6).このことは第1回でも「後段のディジタル・フィルタによる量子化ノイズ低減」という項で簡単に示しました.

$\Sigma\Delta$型ADCで用いられる平均化フィルタは,構成としては「足して平均をとる」という動作をする原理的にはとても簡単なものです.「移動平均」という用語を聞くことがあると思いますが,それとまったく同じです.図6にも中央のブロックで示しています.

$\Sigma\Delta$型ADCのサンプリング周波数$f_{CLK}$(これまで動作クロックMCLKと示したもの)で出力される1ビット・データを$16ビット\times N$や$24ビット\times N$にビット拡張して($N$は$\Sigma\Delta$変調器の次数),平均化計算を行います(実際の計算方法はCICフィルタを使って簡略化されている.これが“$\times N$”の理由.稿末の[4]を参照).

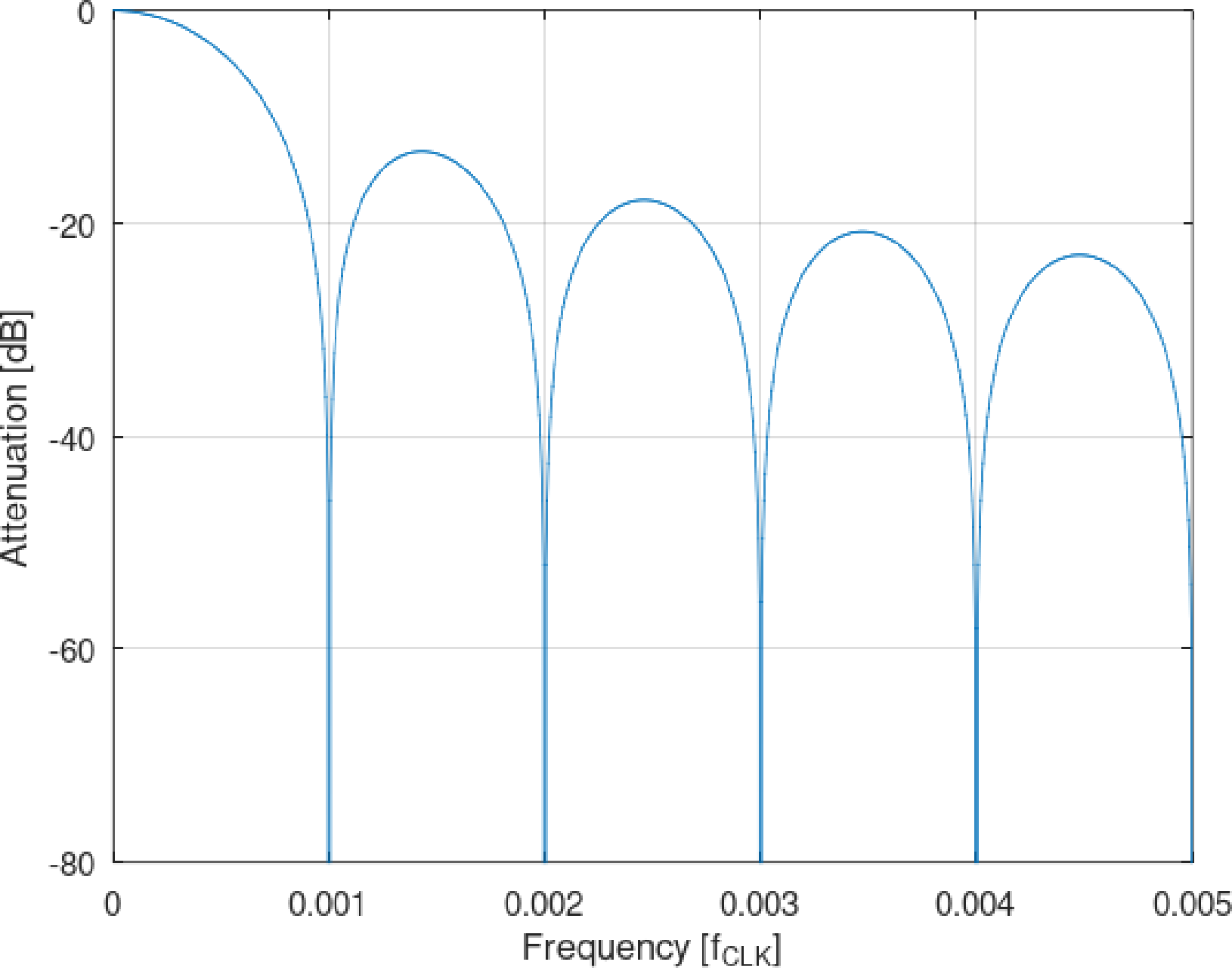

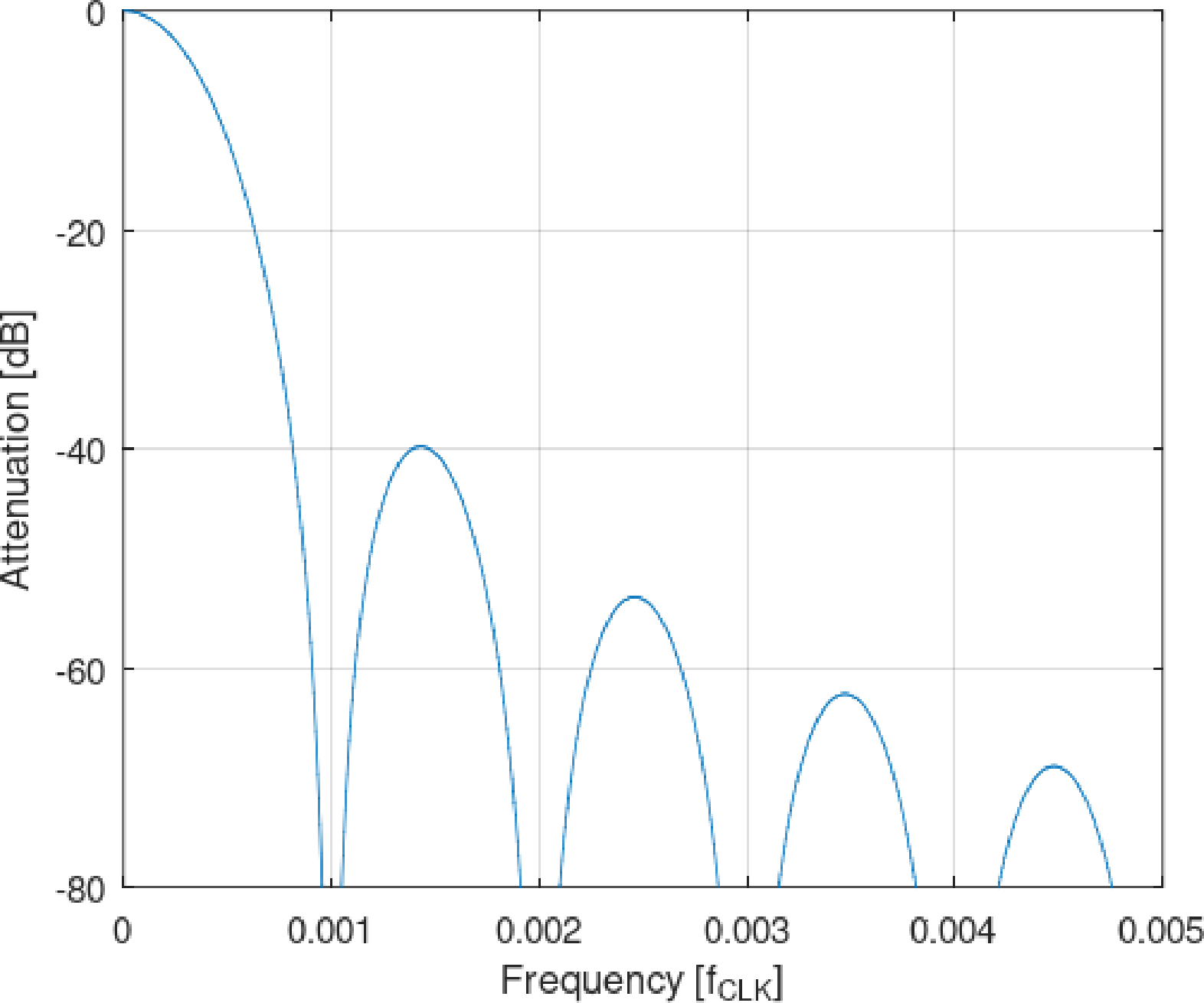

平均化フィルタの入出力を周波数特性として見てみると,図7のようになります(縦軸は[dB]).

これは1000回平均化した例であり,サンプリング周波数$f_{CLK}$の1/1000の周波数に伝達特性がゼロになる点が形成され,$f_{CLK}/1000$の周波数スパンでこれが繰り返されています.

この形状を$\mathrm{sinc}$形状[$\mathrm{sinc}(x) = \sin (x)/x$]と呼びます.実際の$\Sigma\Delta$型ADCでは,これを図8のように複数段縦続に接続して,フィルタの減衰特性をより高めます.

3段縦続に接続した$\mathrm{sinc}^3$フィルタの特性を図9に示します(縦軸は[dB]).

平均化数$M$を増やせば,伝達特性がゼロとなる周波数が$f_{CLK}/M$と低くなり,より狭帯域なフィルタを実現できます.フィルタ出力はレートが間引きされ,その出力データレート$ODR$(Output Data Rate.単位はHz)は式(1)のように表されます.

\begin{equation}

\begin{aligned}

ODR = \frac{f_{CLK}}{M}

\end{aligned}

\label{eq:1-1-1}

\end{equation}

これは伝達特性がゼロになる周波数と等しくなります.平均化を増やせばフィルタが狭帯域になることから,$ODR$も低くてよいという関係です.

|

|---|

| 図10 $\Sigma\Delta$変調器の次数によるノイズ・シェーピングの特性と,それを$\mathrm{sinc}$フィルタで低域だけを取り出す($f_{CLK} = 10 \; \mathrm{MHz}$の例) |

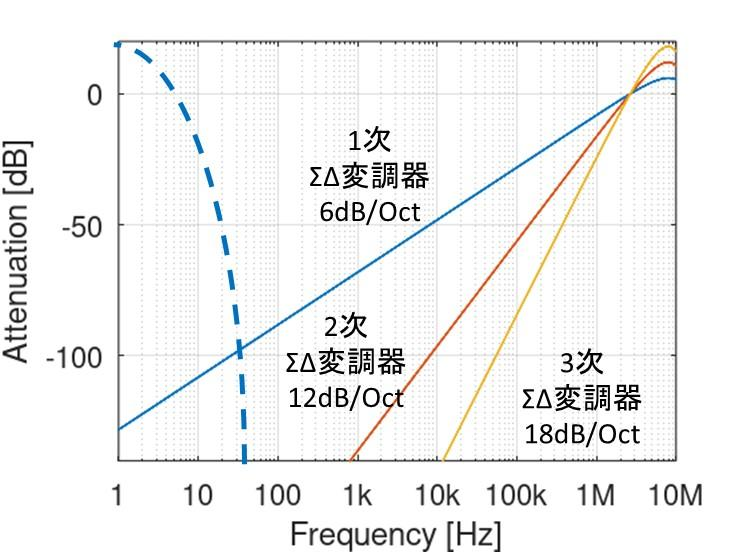

図10に,$\Sigma\Delta$変調器の次数ごとのノイズ・シェーピングの特性を示します.

$\Sigma\Delta$変調器には2次,3次などと,より高次のものがあります.これもこれまで説明してきた1次の$\Sigma\Delta$変調器を縦続接続したものとして考えることができます.この次数が高くなると,この図のようにノイズ・シェーピングの急峻さが高まり,$\mathrm{sinc}$フィルタの帯域を狭くしなくても,量子化ノイズが低減していることがわかります.

ここでさらに$\mathrm{sinc}$フィルタの平均化数を高める,つまり帯域を狭帯域にして$ODR$を低くすれば,量子化ノイズと入力段に存在する物理的な回路ノイズが減って,より高い$SNR$の信号検出が可能になります.

なおよくある質問ですが,ノイズ・シェーピング自体は量子化ノイズに対して働くしくみであり,ADC入力段に存在する物理的な回路ノイズは低減されません.

参考文献

- David Krakauer, 「デジタル・アイソレータの構造」, 技術記事 MS-2234, アナログ・デバイセズ.

https://www.analog.com/media/jp/technical-documentation/tech-articles/MS-2234_jp.pdf - 石井 聡, 「DACの妙技『MIX MODE』をデジタル信号処理の理論的視点から考える」, TNJ-014, 回路設計WEBラボ, アナログ・デバイセズ.

https://www.analog.com/jp/resources/technical-articles/tnj-014.html - Wikipedia, 「Zero-order hold」.

http://en.wikipedia.org/wiki/Zero-order_hold - 石井 聡, 「LTspiceでやってみるデジタル・フィルタ解析(前編)― 平均化フィルタの周波数応答と連続信号・離散信号 ―」, TNJ-052, 石井 聡の回路設計WEBラボ, アナログ・デバイセズ.

https://www.analog.com/jp/resources/technical-articles/tnj-052.html - 石井 聡, 「LTspiceでやってみるデジタル・フィルタ解析(後編)― ΣΔADCでの sinc フィルタってホントに sinc? ―」, TNJ-053, 石井 聡の回路設計WEBラボ, アナログ・デバイセズ.

https://www.analog.com/jp/resources/technical-articles/tnj-053.html

« ZEPマガジン前の記事「BluetoothワンチップBM62で作る低雑音ワイヤレス・オーディオ[Vol.2 ディジタル雑音の発生メカニズムと対策]」

ZEPマガジン次の記事「高周波対応シミュレータ Qucsで学ぶアナログ電子回路 超入門[第4回 反射 1/10!角は切り落とす]」 »