MAX10搭載!16ピンDIP FPGA誕生

作る!私のDIPコンピュータ

|

|---|

| 新開発のDIP_FPGAは,コンパクトでブレッドボードに対応し,複雑な機能を実現可能なFPGAボードである 〈著:圓山 宗智〉 |

| 近日開催:[Onsite/Full KIT/data]復刻!インテル4004プロセッサとビジコン社電卓141-PF |

| 画像クリックで動画を見る.または記事を読む |

MAX10搭載の16ピンDIP FPGAの特徴

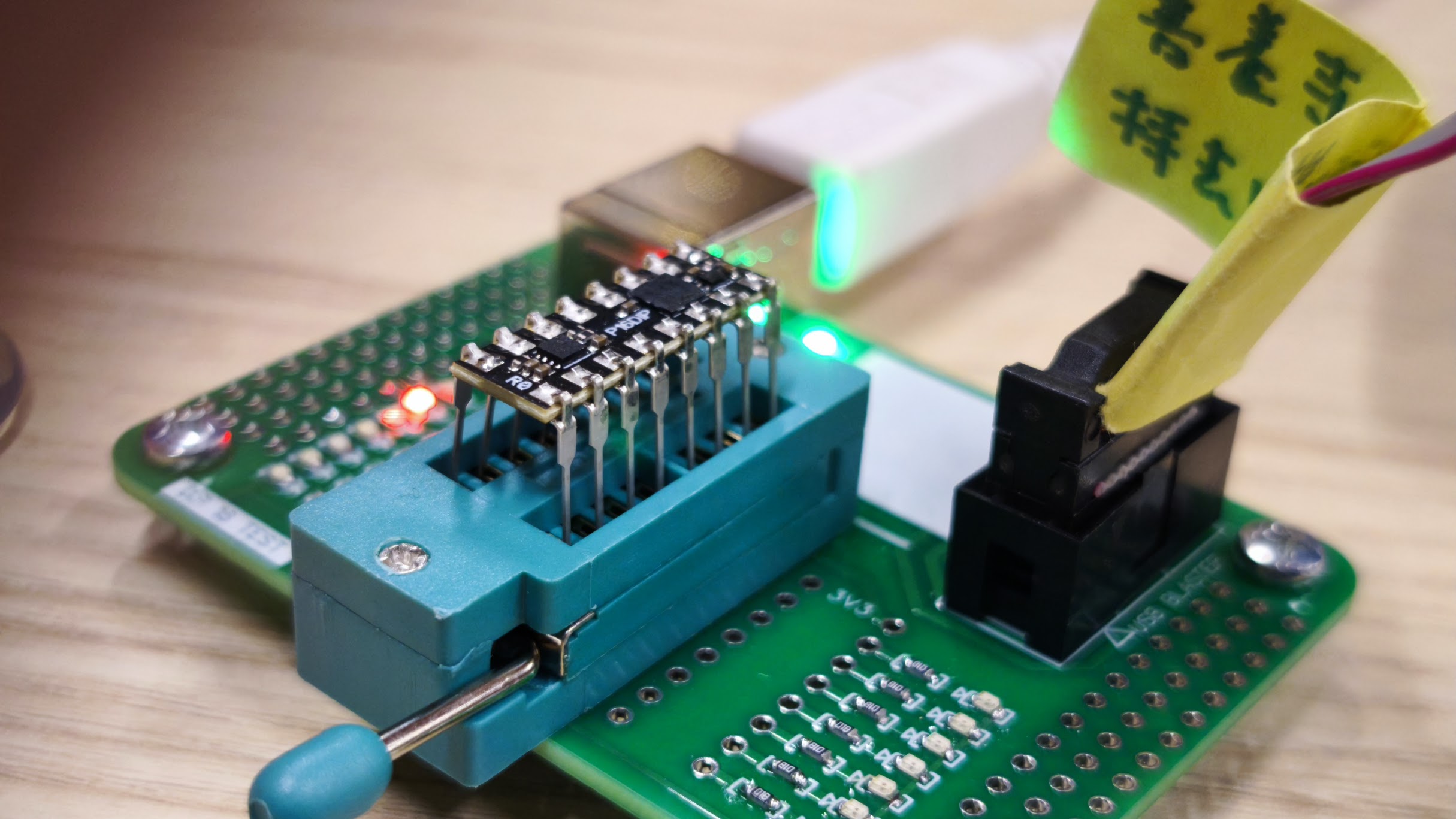

今回紹介するのは,ZEPエンジニアリングが開発した16ピンDIPパッケージのFPGAモジュールです.搭載されているFPGAはAltera社のMAX 10シリーズの中で最小規模の10M02デバイスです.ロジック・エレメント数は2,000個,メモリ容量は108kbitを備えています.PLLが2基,18×18ビットの乗算器が16個搭載されているため,小規模ながら多様な論理回路設計に対応可能です.パッケージは3mm角の36ピンWLCSPで,非常にコンパクトです.

このモジュールは16ピンDIP形状でピン・ピッチは2.54mmです.外部電源は3.3Vで,FPGA内部のコア電圧は1.2Vと2.5Vに対応しています.JTAG端子はユーザI/Oと兼用されているため,Quartus Primeでの設計時には端子機能の設定に注意が必要です.JTAG端子の不適切な割り当てはFPGAの文鎮化を引き起こすことがあるため,注意深い設計が求められます.

コンフィギュレーションと書き込み環境

本FPGAモジュールの特徴的な機能として,磁石を用いたJTAGイネーブル機能があります.搭載されているホールICセンサが磁石の存在を検知すると,JTAGが有効化されてFPGAのコンフィグレーションが可能になります.磁石を取り外すと全ピンがユーザ機能として動作します.このしくみにより,ブレッドボード上での簡単な書き込み操作を実現しています.

書き込み用のDIP_FPGAライタも提供されています.このライタはUSB-Blasterと同等の機能をもち,PICマイコン(PIC18F14K50)を搭載しています.ライタからは3.3Vの電源供給も可能です.磁石を載せてJTAG機能を有効化し,USB経由でFPGAにコンフィグレーション・データを書き込めます.ファームウェアは公開されており,ユーザが容易に利用できます.

設計上の注意事項とトラブル対策

JTAG兼用端子の信号割り当てはAltera MAX 10の仕様上,合成時に明示的に入出力方向を設定しなければなりません.特にTDI,TMS,TCK端子は必ず入出力のいずれかに割り当て,TDO端子は必ず出力に設定してLowまたはHighレベルを出力する必要があります.これを守らない.pofファイルを書き込むとFPGAが認識不能となり文鎮化します.

文鎮化した場合は,基板裏面のnCONFIG信号端子に細い配線をはんだ付けし,USB-BlasterでnCONFIGをグラウンドに落としてリセットできます.この作業は非常に繊細なため,周辺回路を傷つけないよう細心の注意が必要です.まずは.sofファイルでSRAMへのコンフィグを試し,問題がなければ.pofファイルでフラッシュ・メモリに書き込む手順を守ることが推奨されます.

- JTAG端子の設定はQuartus Primeで明示的に行う

- .sofファイルでのSRAMコンフィグを先に行う

- 問題がなければ.pofファイルでフラッシュ書き込み

- 文鎮化時はnCONFIG信号を利用して復旧を試みる

参考文献

- [VOD/KIT/data]新人技術者のためのRISC-V CPU設計 初めの一歩,ZEPエンジニアリング株式会社.

- [VOD/KIT]一緒に動かそう!Lチカから始めるFPGA開発【基礎編&実践編】,ZEPエンジニアリング株式会社.

- [VOD/KIT]Xilinx製FPGAで始めるHDL回路設計入門,ZEPエンジニアリング株式会社.

- [VOD/KIT]Zynqで初めてのFPGA×Linux I/O搭載カスタムSoC製作,ZEPエンジニアリング株式会社.

« ZEPマガジン前の記事「フレーム前後の点群位置を補正する高精度地図生成アルゴリズム」

ZEPマガジン次の記事「計測のための24ビット$\Sigma\Delta$型A-Dコンバータ活用[第3回:低ノイズA-D変換システムの設計]」 »