計測のための24ビット$\Sigma\Delta$型A-Dコンバータ活用[第3回:低ノイズA-D変換システムの設計]

SAR ADCの量子化雑音とシステム全体の雑音を解析

- 著者・講師:石井 聡 / Satoru Ishii(アナログ・デバイセズ)

- 協力:DigiKey

- 企画・編集:ZEPエンジニアリング株式会社

【Index】

計測用途において,24ビットの$\Sigma\Delta$(シグマ・デルタ)型A-Dコンバータ(ADC)は高精度な信号変換を実現できるため注目されています,このADCはノイズ・シェーピング技術を活用し,量子化ノイズを抑制することで高い分解能を達成しています.

本稿では,第3回として低ノイズADCシステム設計の一般論に焦点を当て,特に逐次比較型ADC(SAR ADC)の量子化ノイズと内部ノイズを解析し,アナログ・フロントエンド(AFE,Analog Front-End)を含めた全体のノイズ最適化手法を解説します.SAR ADCには量子化ノイズと内部回路ノイズが存在するため,これらを含むシステム全体のノイズを正確に評価し,適切なADC選定とAFE設計が不可欠です.

基本は,ADCの分解能ビット数に比例して$SNR$(信号対雑音比)が向上しますが,実際にはOPアンプなどのAFEの内部回路ノイズが加わり,これがADCの入力換算ノイズとして影響します.システム全体の雑音指数は,次の2つのアプローチによって最小化できます.

- AFE自体をロー・ノイズ化し,AFEの出力ノイズとADCの入力換算ノイズの比率を適切に設定し,信号源抵抗で生じる熱ノイズがADC入力で支配的になるように設計する

- AFEのノイズ密度と帯域幅を考慮し,ナイキスト帯域内にノイズを制限する

この設計指針は,医療機器や精密計測機器など,特に高分解能と低ノイズが求められる分野において有効です.またLTspiceなどのシミュレーション・ツールを用いたノイズ解析は,実際の製品開発での性能予測に役立つでしょう.〈著:ZEPマガジン〉

1.はじめに

1回目と2回目では,高分解能を可能にするA-D(Analog-to-Digital)コンバータ(本稿では「ADC」と呼ぶ)である,$\Sigma\Delta$(シグマ・デルタ)型ADCの「ノイズ・シェーピング技術」について説明してきました.

今回は,逐次比較型ADC(本稿では「SAR ADC」と呼ぶ.SARはSuccessive Approximation Register:逐次比較)で生じる量子化誤差電圧(量子化ノイズ)の大きさを示し,ここからアナログ・フロントエンド(センサからADCの入力までのアナログ回路.以降AFEと呼ぶ)も含めて,適切なADCの選定基準とシステム全体でノイズ性能を最適化する方法について説明します.

2.ADCで生じる量子化ノイズと理論$SNR$

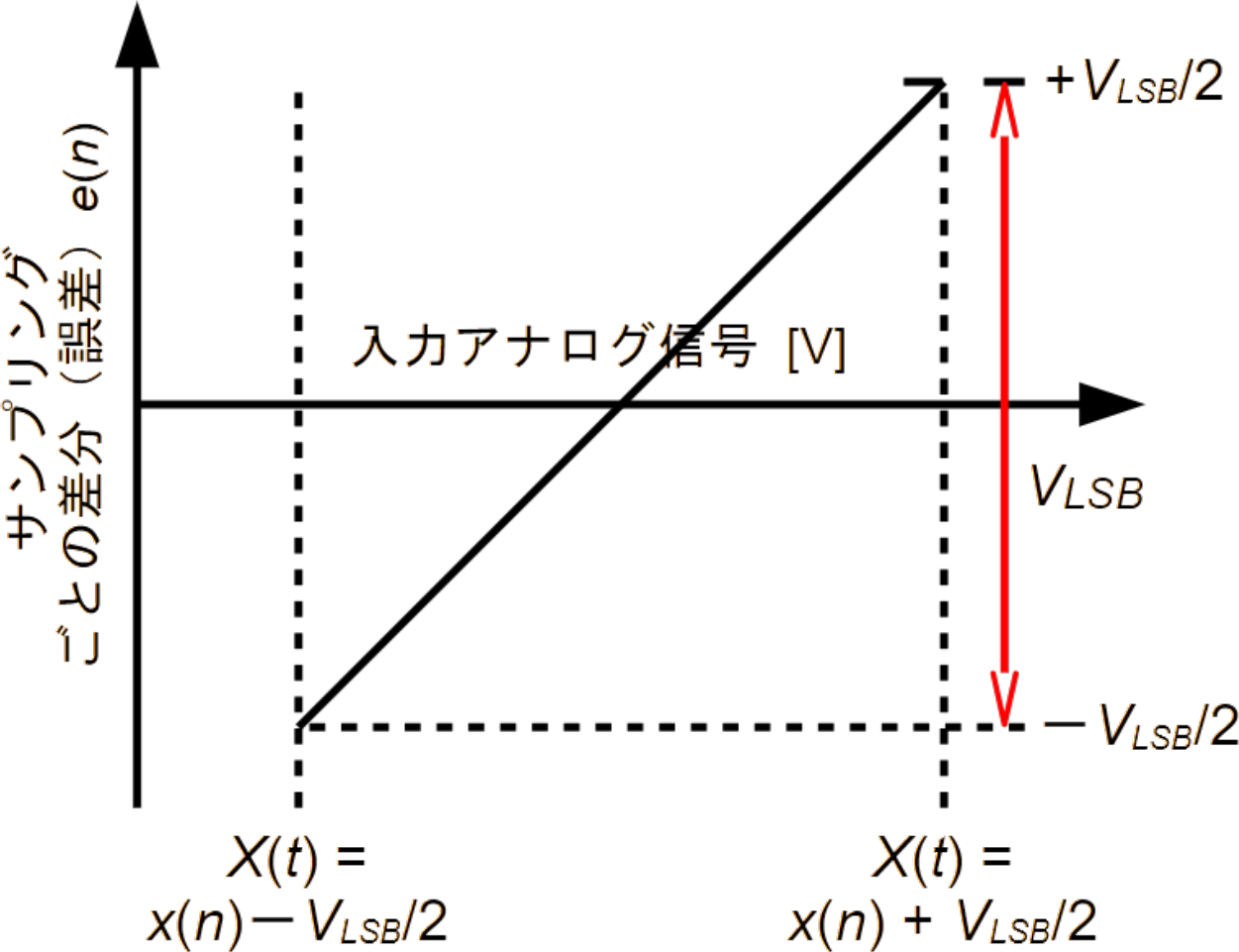

SAR ADCでも,入力アナログ信号$X_{IN}(t)$が離散ディジタル値$x(n)$に変換されることで,この差分[式(1)]が量子化ノイズに相当する量子化誤差になります.

\begin{equation} \begin{aligned} e(n) = X_{IN}(t) – x(n) \end{aligned} \label{eq:1-1-1} \end{equation}

ディジタル値$x(n)$はとびとびの値,つまり離散値しか取れないからです.ここで,$t$は連続時間,$n$はサンプル数ですが,連続時間と離散時間をつなぐ意味合い(厳密ではなくイメージ)で上記の式を示しています.

この$e(n)$が「量子化ノイズ」です.量子化ノイズはSAR ADCの最小ビット分解能$V_{LSB}$ [V]($V_{LSB} = V_{FS}/2^{N}$.ここで$V_{FS}$はADCのフルスケール入力電圧範囲,$N$は分解能ビット数)の$\pm V_{LSB}/2$ [V]範囲に図1のように一様に分布しています.

これを自乗し積分して実効値として計算すると,式(2)で表される量子化ノイズの実効値$q$が得られます.

\begin{equation} \begin{aligned} q = \frac{V_{LSB}}{\sqrt{12}} = \frac{V_{FS}}{\sqrt{12} \cdot 2^N}\;\mathrm{[V_{RMS}]} \end{aligned} \label{eq:1-1-2} \end{equation}

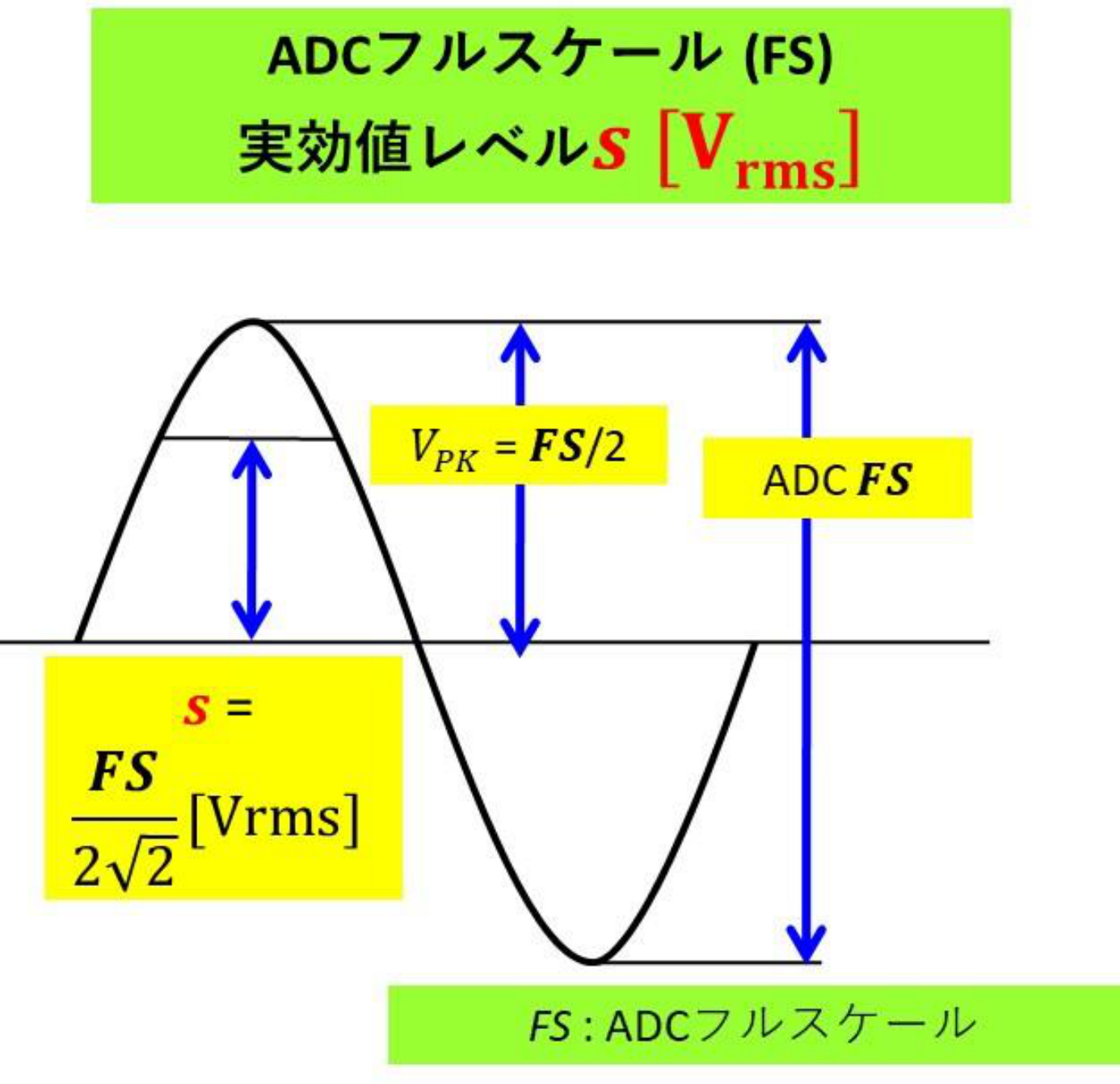

つぎに入力信号をフルスケール電圧としたときの量子化ノイズに対する理論$SNR$(Signal to Noise Ratio; 信号対ノイズ比)$SN_Q$を計算してみると,式(3)のようになります.

\begin{equation} sn_Q = \frac{(s)^2}{(q)^2} = \dfrac{(V_{FS}/2\sqrt{2})^2}{V^2_{LSB}/12} = \dfrac{(V_{FS}/2\sqrt{2})^2}{\left(\dfrac{V_{FS}}{\sqrt{12}\cdot2^N}\right)^2} = \left(\frac{\sqrt{12}\cdot2^N}{2\sqrt{2}}\right)^2 = \frac{12}{8}2^{2N} \label{eq:1-1-3} \end{equation}

ここで$s$はフルスケール入力電圧(正弦波のピーク・ツー・ピーク電圧)の実効値で,フルスケール電圧の1/(2$\sqrt{2}$)になります(図2).

式(3)で自乗しているのは,$SNR$は電力の次元で考えるからです.これをdBに変換すると,式(4)のようになります.

\begin{equation} \begin{aligned} SN_Q = 6.02 \times N + 1.76\;\mathrm{[dB]} \end{aligned} \label{eq:1-1-4} \end{equation}

dBで分解能ビット数$N$に比例した理論$SNR$が得られることがわかります.たとえば14ビットADCでは$SN_Q = 86 \; \rm{dB}$になります.

3.ADCでの入力換算ノイズ

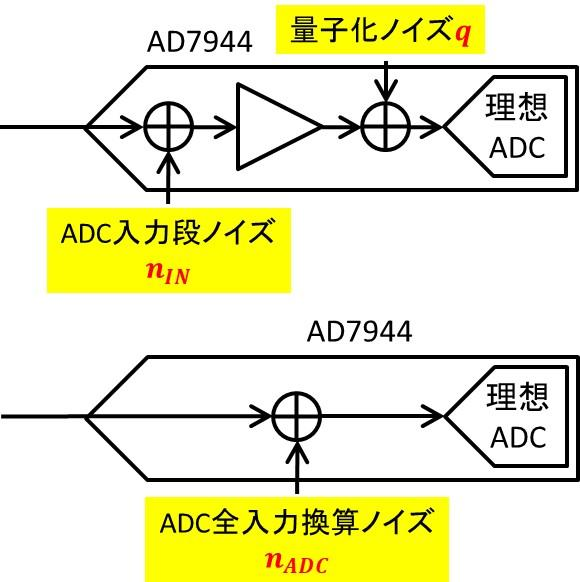

ここまでの説明は,ADC内部のノイズ源は量子化ノイズ$q$以外には無いとして考えてきました.しかし実際はOPアンプなどと同様,ADC入力段の電子回路でノイズが生じ,これがADCの入力段換算ノイズ$n_{IN}$として追加されます.

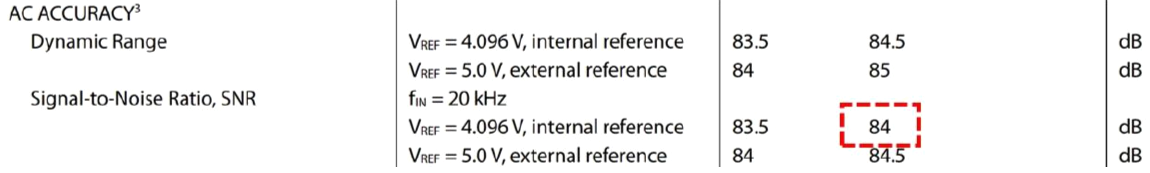

たとえば14ビットSAR ADC AD7944では,図3のように$SNR$のスペックは84 dBです(理論$SNR$ $SN_Q$より2 dB悪い).

これからADCの全入力換算ノイズ(電圧実効値)$n_{ADC}$を計算してみると(フルスケール電圧$V_{FS} = 4.096 \; \rm{V}$を用いて),式(5)が得られます.

\begin{equation} \begin{aligned} n_{ADC} = \frac{4.096}{2\sqrt{2}} \div 10^{84/20} = 91.4\;\mathrm{\mu V_{RMS}} \end{aligned} \label{eq:1-1-5} \end{equation}

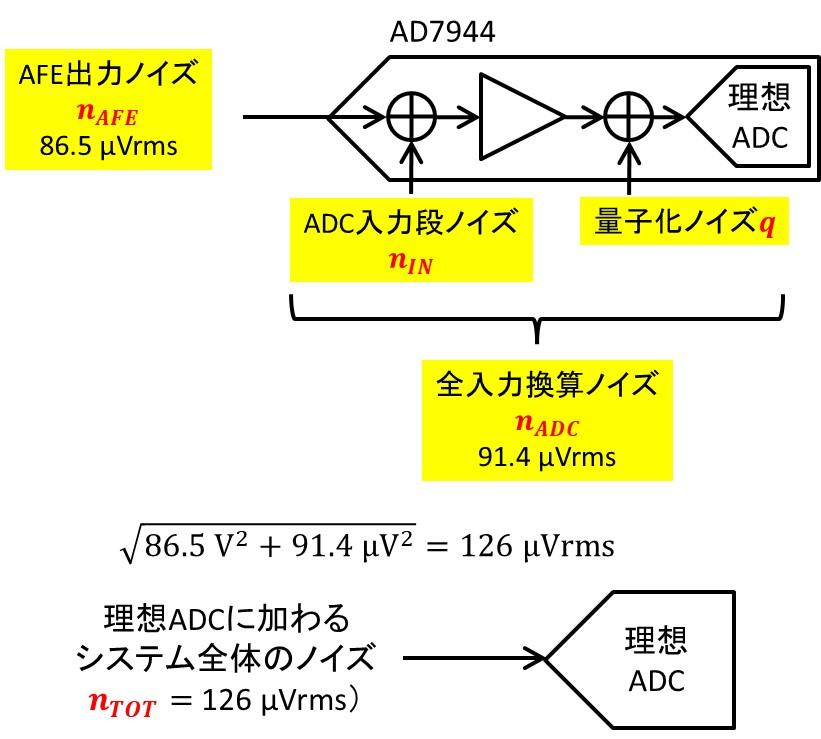

$n_{ADC}$は量子化ノイズ電圧$q$と,ADC入力段ノイズ$n_{IN}$を自乗和平方根(Root Sum Square:RSS)で式(6)のように合算します.ノイズの合算は単純な足し算ではありません.

\begin{equation} \begin{aligned} n_{ADC} = \sqrt{q^2 + n_{IN}^2} \end{aligned} \label{eq:1-1-6} \end{equation}

ここで,$q$は量子化ノイズ電圧の実効値,$n_{IN}$はADC入力段ノイズをADCの入力換算(電圧実効値)したものです.これをシステム図として表すと図4となります.

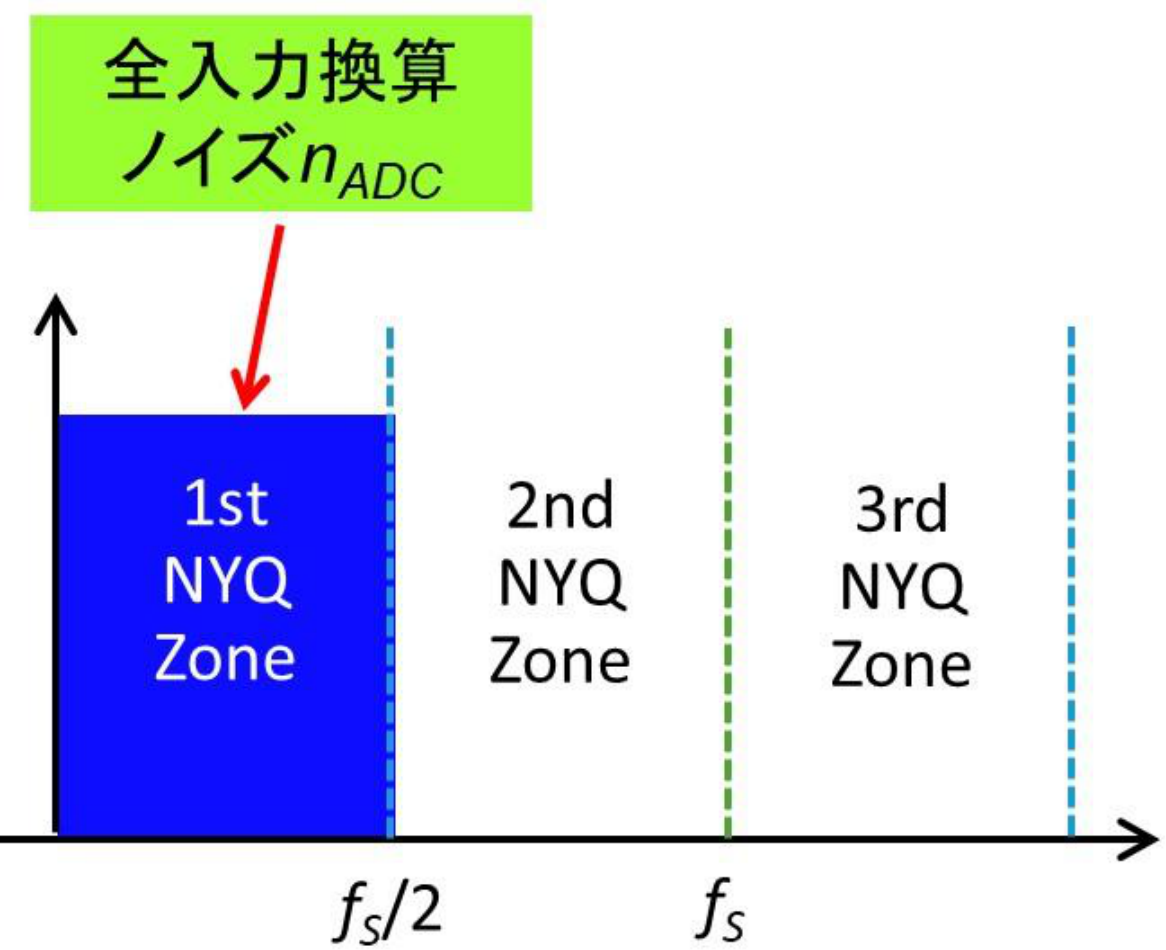

SAR ADCにおいては,全入力換算ノイズ$n_{ADC}$は図5のようにサンプリング周波数$f_S$の半分のナイキスト帯域$f_S /2$に存在していると定義されます.

4 アナログ・フロントエンド(AFE)からのノイズを考慮する

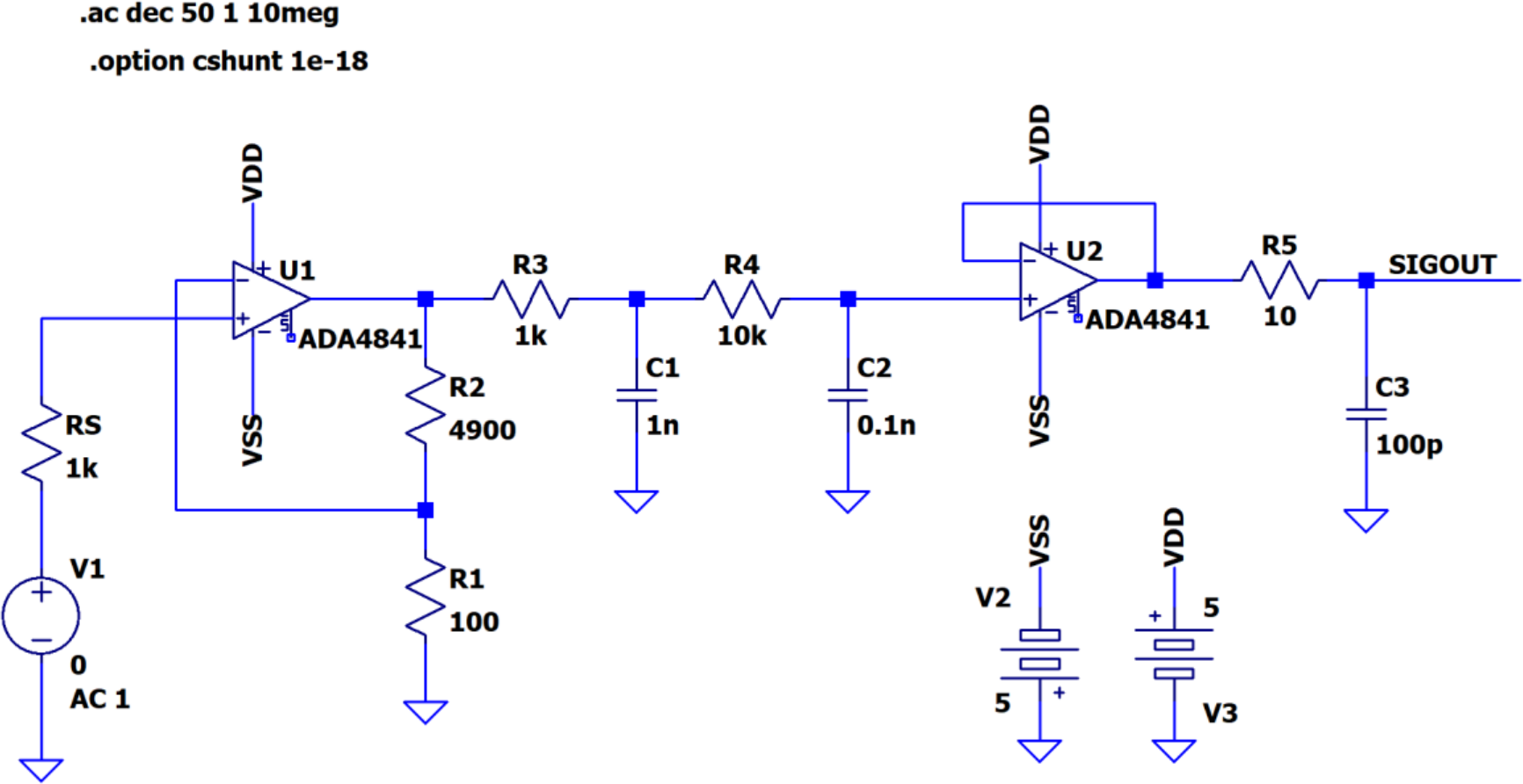

ADCにAFEを接続したことを考えます.図6のような信号源抵抗1 k$\Omega$をもつセンサ信号を増幅し,帯域制限したAFEを例にします.

ADCでの折り返し(エイリアシング)が生じないように,一般的にAFEではエイリアシング・フィルタにより,ナイキスト帯域$f_S /2$以下の帯域幅に帯域制限します(図6の$R_3,R_4,C_1,C_2$).

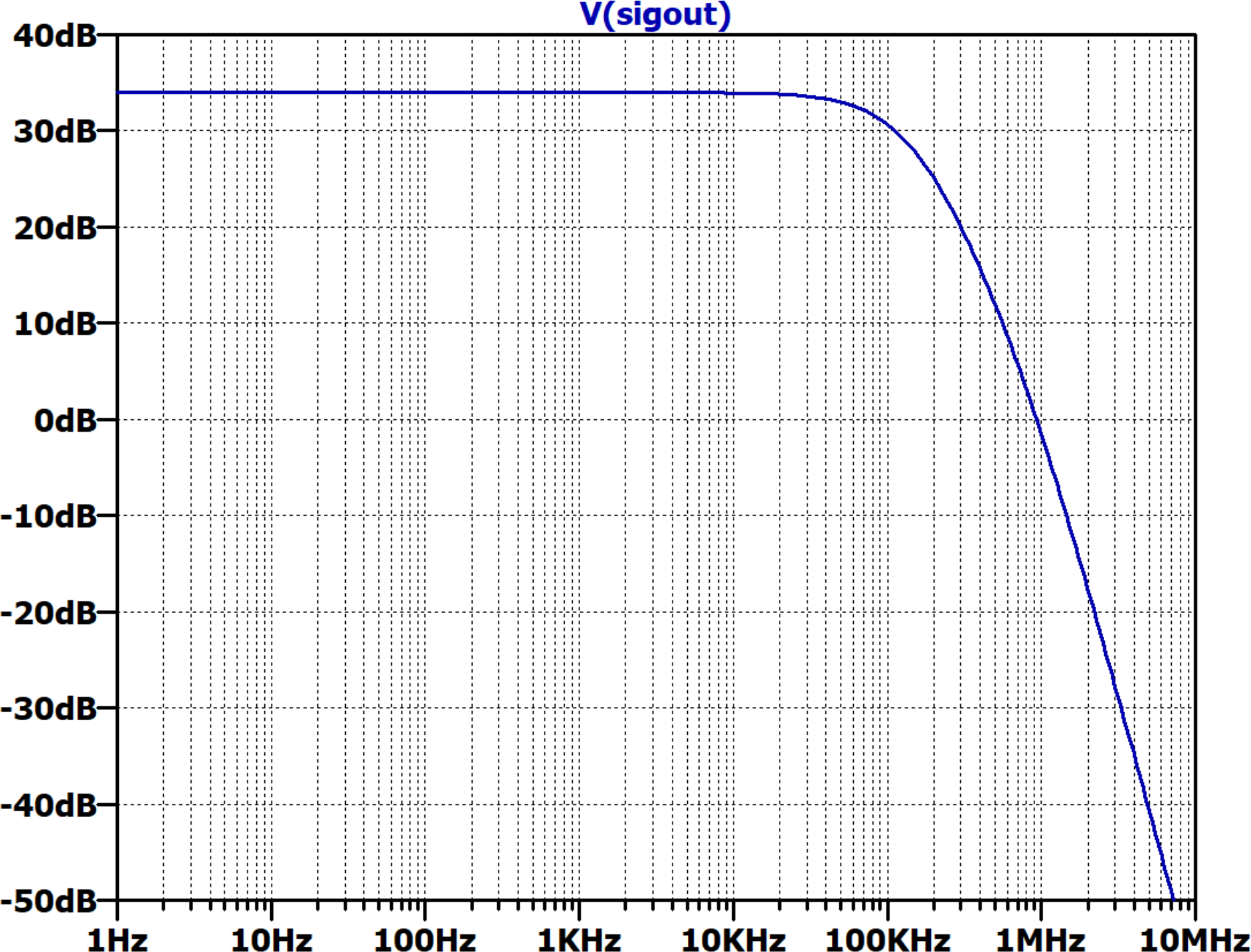

図7は,LTspiceでシミュレーションしたこのAFEの周波数特性です.

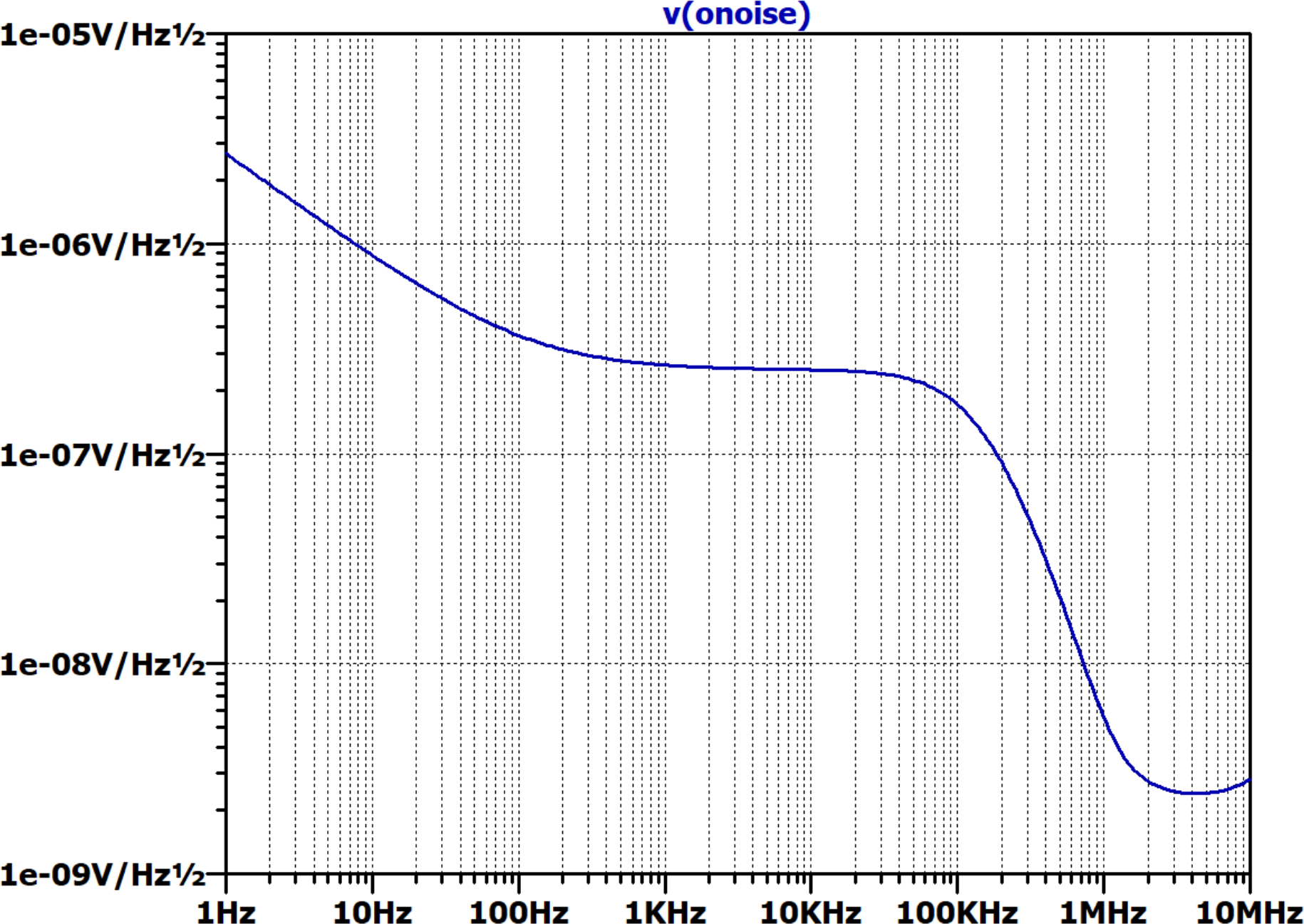

図8はAFEの出力ノイズ密度特性です.

AD7944で2 Mspsでサンプリングすることを考えると,AFEの周波数特性$-$3 dB帯域が95.5 kHz(ナイキスト周波数で$-$35 dBの減衰),出力ノイズ密度$-$3 dB帯域が85.7 kHzであり,ともども十分ナイキスト帯域$f_S /2 = $1 MHz以下になっています.

ADC入力に加わるノイズは,図9で示しているAFEの「出力」ノイズです.

ADCの全入力換算ノイズ(実効値)と比較できるようにするためには,図8の密度([V/$\sqrt{\rm{Hz}}]$)の次元ではなく,このAFE出力の全ノイズ(電圧実効値)$n_{AFE}$ $\rm{[V]}$を求める必要があります.これはLTspiceでは簡単に実現できて,CTRLキーを押しながらラベルv(onoise)をクリックすればよいのです.この場合の結果は$n_{AFE} = 86.5 \; \rm{\mu V}$と実効値が得られました.

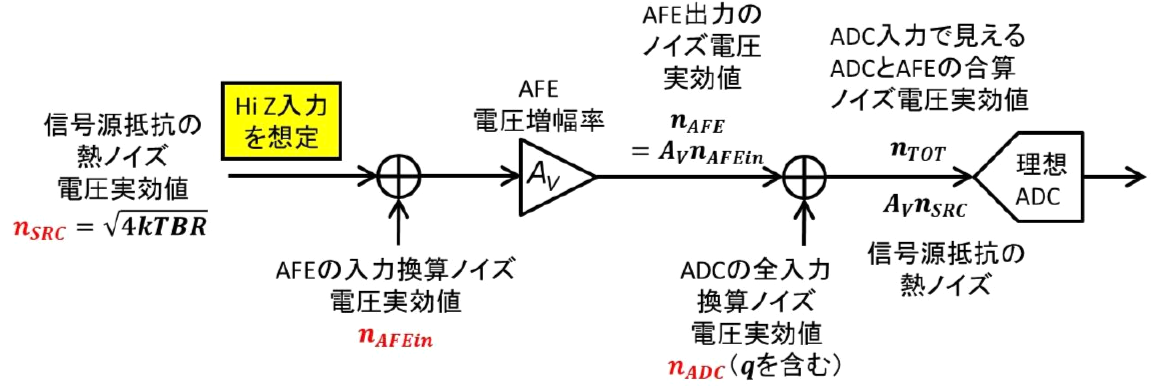

このAFEのノイズを含めたシステム全体のノイズ$n_{TOT}$は図9のように表すことができます.ノイズどうしは自乗和平方根(RSS)で計算(合算)します.

これからフルスケール入力電圧(正弦波のピーク・ツー・ピーク電圧 4.096 V$_\mathrm{P-P}$)の実効値($\mathrm{1.45 \; V_\mathrm{RMS}}$)に対する$SNR$ $SN_{TOT}$を計算すると,式(7)が得られます.

\begin{equation} \begin{aligned} sn_{TOT} &= \frac{(s)^2}{(n_{TOT})^2} = \left(\frac{1.45\;\mathrm{V_{RMS}}}{126\;\mathrm{\mu V_{RMS}}}\right)^2 = 132 \times 10^6 \end{aligned} \label{eq:1-1-7} \end{equation}

これをdBに変換すると$SN_{TOT} = 81.2 \; \rm{dB}$と計算できます.

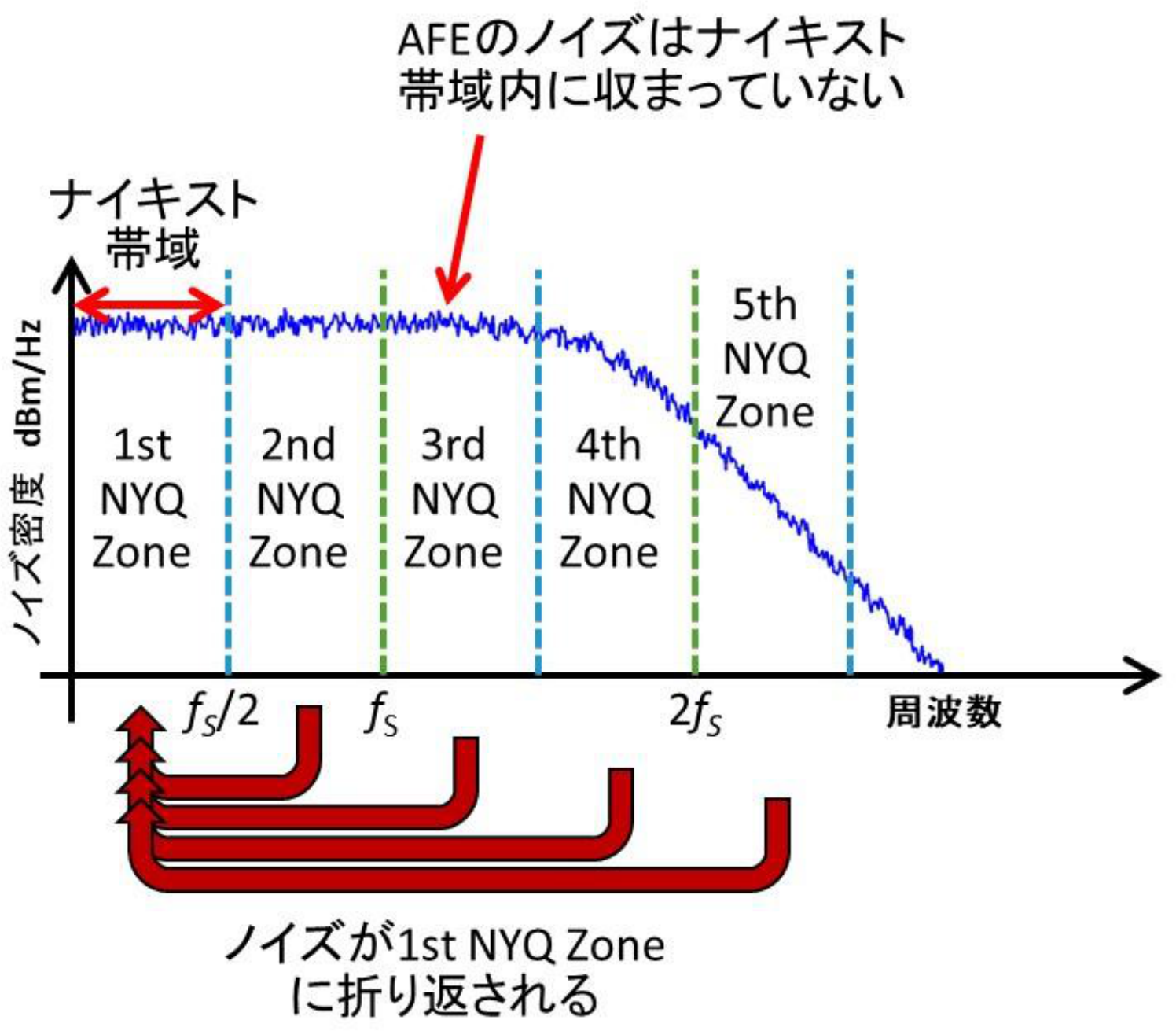

AFEのノイズがナイキスト帯域を超えて分布している場合

ここまではAFEのノイズがナイキスト帯域内に収まっているという前提で話しを進めてきました.しかし場合によっては,ノイズが分布する帯域がナイキスト帯域を超えている場合もあるでしょう.

これを図10に示します.

この場合は,AFEの各高次ナイキスト帯域内のノイズがすべて基本ナイキスト帯域($f_S/2$以下)に折り返されてきます.ADCが検出するAFEのノイズが増大することになります.

折り返された合算のAFEノイズ実効値の計算も自乗和平方根(RSS)で行います.実際のやり方は,LTspiceのノイズ・シミュレーションの結果を各ナイキスト・ゾーンの領域ごとに表示させ,その領域での全ノイズ実効値をCTRLキー+右クリックで計算し,それぞれの数字を自乗和平方根で足し合わせます.これがADCが検出する折り返しも考慮したAFEの全ノイズ(電圧実効値)$n_{AFE}$になります.

4.ノイズ・レベルと逐次比較型ADCの有効ビット分解能

得られた$SNR$から「有効ビット分解能」Effective Number of Bits; $ENOB$というものを計算できます.これはさきの理論$SNR$ $SN_Q$の式を変形することで,式(8)が得られます.

\begin{equation} \begin{aligned} ENOB = \frac{SN_{TOT} – 1.76}{6.02} \end{aligned} \label{eq:1-1-8} \end{equation}

今回のAFEとAD7944を用いたシステムでは,式(9)のように計算できます.

\begin{equation} \begin{aligned} ENOB = \frac{81.2\;\mathrm{dB} – 1.76}{6.02} = 13.2\;\mathrm{bit} \end{aligned} \label{eq:1-1-9} \end{equation}

この結果から,13.2ビットまで有効であることがわかります.14ビットのADCを用いても,その分解能に近い性能が実現できていることがわかります.

ビット数が大きい高分解能のADCを用いれば,ADCの全入力換算ノイズ(実効値)$n_{ADC}$は低減します.しかし上記の式のように有効ビット分解能をADCに見合った値にするためには,AFEの出力ノイズ$n_{AFE}$を,ADCの全入力換算ノイズ(実効値)$n_{ADC}$に相当する程度に低減させる必要があることがわかります.この低減をどの程度にするかは,あらためて以降に示します.

5.AFE出力ノイズとADC全入力換算ノイズの比率をどうすればよいか

「AFEの出力ノイズ$n_{AFE}$を,ADCの全入力換算ノイズ(実効値)$n_{ADC}$に相当する程度に低減させる必要がある」と示しました.この最適ポイントがどこになるかを示します.基本は,「ADC入力で,信号源抵抗で生じるノイズができるだけ支配的になるように設定する」ということです.

図11は信号源抵抗で生じる熱雑音実効値$n_{SRC}$を源とし,ADCを理想的なものとしてADCに加わる各ノイズ源を示したものです.AFEの電圧増幅率を$A_V$,またAFEのノイズは入力換算にしています($n_{AFEin} = n_{AFE}/A_V$).

このようにしたとき,系で加わる付加ノイズの指標「雑音s指数$F$(Noise Factor)」は式(10)のようになります.導出仮定は長くなるので割愛します.

\begin{equation} \begin{aligned} F = 1 + \frac{n^2_{AFEin}}{n^2_{SRC}} + \frac{n^2_{ADC}}{A^2_V n^2_{SRC}} \end{aligned} \label{eq:1-1-10} \end{equation}

$F$は1に近いほど良好で,システム全体で信号源抵抗で生じる熱ノイズが支配的,つまり取り除けないノイズしかADCで見えない状態になります.なお$F$をdBで表したものをNoise Figure $NF$と呼びます(こちらがよく使われる).

式(10)を吟味してみると,1つはAFEの入力換算全ノイズ$n_{AFEin}$が信号源抵抗で生じる熱ノイズ実効値$n_{SRC}$に対して小さくなるように(できるだけ)AFEの低ノイズ化を図ること,もう1つは「ADCの全入力換算ノイズ(実効値)$n_{ADC}$」が,「信号源抵抗で生じる熱ノイズ実効値がAFEで$A_V$倍で増幅されADCで検出されるノイズ量$A_V n_{SRC}$」に対して小さくなるように$A_V$を設定することです.この第3項は1/2~1/4程度になれば十分です.

最終的には得られた結果から,有効ビット分解能$ENOB$を計算し検算します.信号源ノイズがADC入力で大きめに見えますので,この設定方法による$ENOB$は使用するADCの分解能よりいくぶん低下します.

信号源抵抗で生じる熱ノイズ実効値nSRCを求めるには

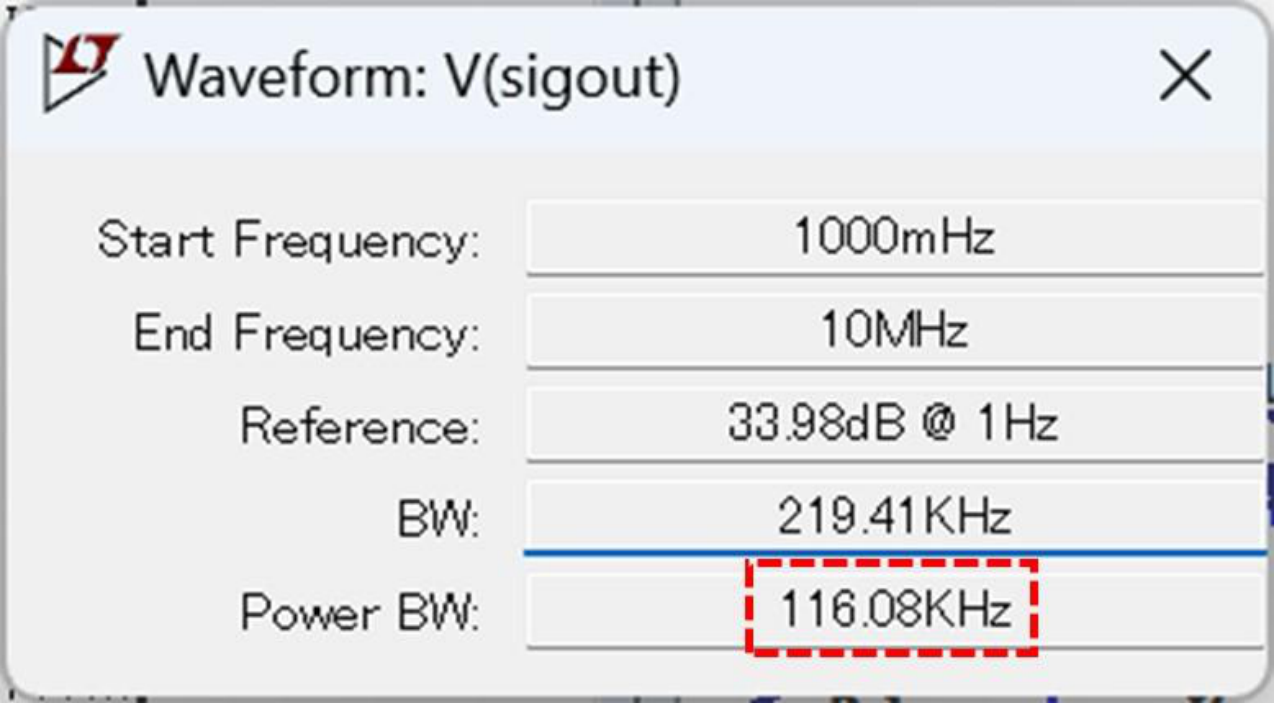

ADCで検出される信号源抵抗で生じる熱ノイズ実効値$n_{SRC}$を求めるには,図12のようにLTspiceでAC解析により周波数特性をシミュレーションし,CTRL+右クリックで出てくるPower BWの数値を用いて,式(11)のように計算します.

\begin{equation} \begin{aligned} n_{SRC} = \sqrt{4kTBR} \end{aligned} \label{eq:1-1-11} \end{equation}

ここで,$k$はボルツマン定数($1.38 \times 10^{23}) \; [\rm{J/K}]$,$T$は絶対温度[K],$B$はLTspiceで求めたPower BWの数値[Hz],$R$は抵抗値[$\Omega$]です.信号帯域幅がADCのナイキスト帯域に収まらない場合でも,上記に説明した自乗和平方根を用いることなく,すでにPower BWの数値だけでその計算が済んでいます.

ディジタル・フィルタで帯域制限する場合は

A-D変換したあとにディジタル領域でディジタル・フィルタをかけて,帯域制限をするケースも多くあるでしょう.この際のAFE出力ノイズ$n_{AFE}$とADC入力換算ノイズ$n_{ADC}$の比率の考え方は基本的には先の説明と同じです

しかしディジタル領域での帯域制限を考慮に入れる必要があるため,ディジタル・フィルタの通過周波数領域でAFE出力ノイズとADC入力換算ノイズを1Hzノイズ密度にして,密度スペクトルとして(特定周波数領域に着目して)考えます.

LTspiceのシミュレーションでは,AFE出力ノイズはもともと1Hzノイズ密度でした.そのためこれは問題ありません.一方でADC入力換算ノイズは全ノイズ$n_{ADC}$として実効値で表されています.これを1Hzノイズ密度$n_{ADC \rm{1Hz}}$にするには式(11)のように計算します.

\begin{equation} \begin{aligned} n_{ADC1Hz} = \frac{n_{ADC}}{\sqrt{f_S/2}} \end{aligned} \label{eq:1-1-12} \end{equation}

ここで$f_S /2$はナイキスト帯域です.

参考文献

- David Krakauer, デジタル・アイソレータの構造, 技術記事 MS-2234, アナログ・デバイセズ. https://www.analog.com/media/jp/technical-documentation/tech-articles/MS-2234_jp.pdf

- 石井 聡, DACの妙技『MIX MODE』をデジタル信号処理の理論的視点から考える, TNJ-014, 回路設計WEBラボ, アナログ・デバイセズ. https://www.analog.com/jp/resources/technical-articles/tnj-014.html

- Wikipedia, Zero-order hold. http://en.wikipedia.org/wiki/Zero-order_hold

- 石井 聡, LTspiceでやってみるデジタル・フィルタ解析(前編) ― 平均化フィルタの周波数応答と連続信号・離散信号 ―, TNJ-052, 石井 聡の回路設計WEBラボ, アナログ・デバイセズ. https://www.analog.com/jp/resources/technical-articles/tnj-052.html

- 石井 聡, LTspiceでやってみるデジタル・フィルタ解析(後編) ― ΣΔADCでの sinc フィルタってホントに sinc? ―, TNJ-053, 石井 聡の回路設計WEBラボ, アナログ・デバイセズ. https://www.analog.com/jp/resources/technical-articles/tnj-053.html