Zynq FPGA入門 自作回路とCPUの通信

一時データ保存回路 レジスタの活用

CPUのアドレス空間上にレジスタを配置して自作回路を制御

|

|---|

|

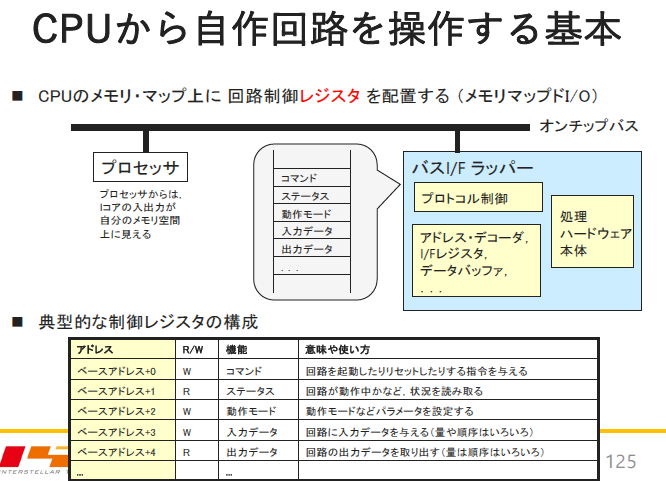

図1 ZynqはCPUと自作回路の通信バスを備える.CPUのアドレス空間上に自作回路を制御するレジスタを配置し,このアドレスを利用するメモリ・マップトI/O方式で自作回路を制御する.画像クリックで動画を見る.または記事を読む.[提供・著]森岡 澄夫 詳細:【Cora Z7-07S Zynq-7000開発ボード付き】Zynqで初めてのFPGA×Linux I/O搭載カスタムSoC製作 |

Zynq FPGAでは,CPUと自作回路の通信を可能にするためにオンチップ・バスを用います.この通信の基本形はメモリ・マップトI/Oです.自作回路の制御用レジスタをCPUのアドレス空間上に配置し,CPUがこのアドレスを介して回路を制御します.制御の対象となるレジスタの典型的な構成は次のようになります.

- コマンド・レジスタ ($\text{Base Address}+0$)

回路をリセットまたは動作開始するための指令を書き込むレジスタ - ステータス・レジスタ ($\text{Base Address}+1$)

回路が動作中であるかなど,現在の状態を読み取るレジスタ - 動作モード設定レジスタ ($\text{Base Address}+2$)

回路の動作モードやパラメータを設定するためのレジスタ - 入力データ・レジスタ ($\text{Base Address}+3$)

回路に対してデータを与えるためのレジスタ - 出力データ・レジスタ ($\text{Base Address}+4$)

計算結果や処理結果を取得するためのレジスタ

このしくみにより,CPUは単純なメモリ操作として回路を操作できます.CPUが掛け算を行うIPコアを操作する場合,次の手順で実行します.

- 初期化

リセット・コマンドを送信して状態をクリアします - データ入力

掛け算の引数を入力データ・レジスタに書き込みます - 計算開始

コマンド・レジスタに動作開始の指令を送ります - 結果取得

ステータス・レジスタを監視し,計算完了後に出力データを読み取ります

ラッパ回路の重要性

オンチップ・バスに自作回路を接続するには,ラッパ回路(Wrapper)を設計する必要があります.このラッパ回路の役割は次のとおりです.

- アドレス・デコード

CPUから送られるアドレスを解釈し,適切なレジスタに対応付けます - データ管理

バス・プロトコルにしたがってデータの読み書きを行います.特に,入力データや出力データの一時保存に対応するため,内部にバッファをもつことが一般的です - プロトコル制御

AXIなどのオンチップ・バス・プロトコルに合わせた制御信号を生成します

これにより,自作回路はCPUから見て一連のメモリ空間として扱えるようになります.

レジスタI/Fの構造と活用

レジスタの役割と分類

自作回路とCPU間の効率的なデータ通信の鍵となるのが,制御用レジスタです.これらのレジスタは一般に次の役割を果たします.

- 制御レジスタ

動作モードや初期化コマンドの設定 - 状態レジスタ

処理回路の現在の状態を提供 - データ・レジスタ

入力データの受け渡しや結果データの提供

この設計により,CPUは簡易かつ直感的に回路を操作できます.レジスタの読み書き操作はシンプルであるため,ソフトウェアからの操作性が向上します.

レジスタの活用例

掛け算IPコアを例に考えると,次のようなシナリオが想定されます.

- CPUは$V_{\text{in}}$や$L_r$といったパラメータを入力データ・レジスタに書き込みます

- コマンド・レジスタを介して「計算開始」の指令を送ります

- 状態レジスタを監視し,回路がアイドル状態になるまで待機します

- 計算結果を出力データ・レジスタから取得します

このような操作フローにより,CPUとFPGA回路間の通信は効率的かつ柔軟なものになります.

効率化のポイント

- バス・プロトコルの理解

AXIなどのプロトコルを熟知し,最適化されたラッパ回路を設計する - レジスタ配置の工夫

アクセス頻度や処理優先度に応じてレジスタの配置を最適化する - エラー・ハンドリング

CPU側で,回路が動作異常を示す場合の例外処理を組み込む

これらを徹底することで,Zynq FPGAを用いたシステムの性能と信頼性を最大限引き出すことが可能です.〈著:ZEPマガジン〉

著者紹介

- NTT,IBM,Sony,NECの各研究所において高性能回路IPやハイレベル・シンセシスの研究,およびプレイステーションなどの製品用SoC開発に従事した後,現職にて民間宇宙ロケットの飛行制御コンピュータの研究開発に従事.FPGAや高位合成を活用している

著書

- [VOD/KIT]一緒に動かそう!Lチカから始めるFPGA開発【基礎編&実践編】,ZEPエンジニアリング株式会社.

- [VOD/KIT]Xilinx製FPGAで始めるHDL回路設計入門,ZEPエンジニアリング株式会社.

- [VOD/KIT]一緒に動かそう!Lチカから始めるFPGA開発【基礎編】,ZEPエンジニアリング株式会社.

- [VOD/KIT]Zynqで初めてのFPGA×Linux I/O搭載カスタムSoC製作,ZEPエンジニアリング株式会社.

- [VOD/KIT]Tiny FPGA実習!高校生から始めるHDLプログラミング,ZEPエンジニアリング株式会社.

- [VOD/Pi KIT]カメラ×ラズパイで一緒に!初めての画像処理プログラミング,ZEPエンジニアリング株式会社.

- スパコンでも破れない!高セキュリティ・マイコン・プログラミング,ZEPエンジニアリング株式会社.

- [YouTube]宇宙軌道ロケット 成功の方程式

- [YouTube]宇宙ロケットの電子回路開発

- FPGA/Zynqで作るカスタム・コンピュータ・チップ,ZEPエンジニアリング株式会社.

- Lチカ入門!ソフトウェア屋のためのHDL事はじめ,ZEPエンジニアリング株式会社.

- USBカメラの動画キャプチャ&描画用 Pythonプログラム,ZEPエンジニアリング株式会社.

- ライブラリ完備!組立式ラズパイI/O増設ボード MCC DAQ HATSファミリ誕生,ZEPエンジニアリング株式会社.

参考文献

- [VOD/KIT] 実習キットで一緒に作る!オープンソースCPU RISC-V入門,ZEPエンジニアリング株式会社.

- [VOD/KIT]ARM Cortex-A9&FPGA内蔵SoC Zynqで初体験!オリジナル・プロセッサ開発入門,ZEPエンジニアリング株式会社.