初めてのHDL記述「組み合わせ回路」

System Verilog,Verilog1995/2001の3とおり

組み合わせ回路の基本概念

|

|---|

|

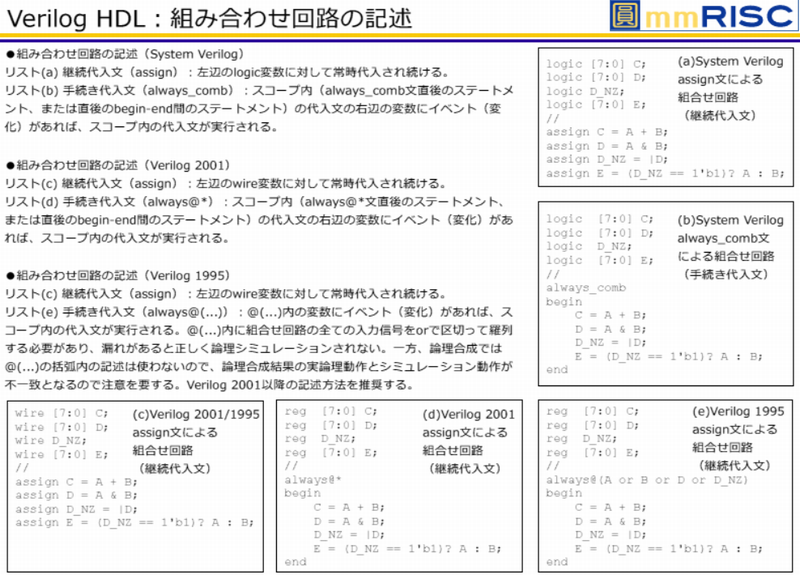

図1 HDLでの組み合わせ回路の記述は,System VerilogやVerilog 1995/2001において2つの方法がある.画像クリックで動画を見る.または記事を読む.[著]圓山宗智 詳細:[VOD]新人技術者のためのRISC-V CPU設計初めの一歩~C言語完全対応!HDLソース500行のミニCPUを一緒に作る~ |

HDLでの組み合わせ回路の記述は,System VerilogやVerilog 1995/2001において大きく2つの方法があります.1つは継続代入文であり,assign文を用いて左辺の変数に常時代入する方式です.もう1つは手続き代入文であり,always_combやalways@*などのブロック内で代入文を記述し,右辺の変数が変化したときにスコープ内の代入文が実行される方式です.

継続代入文では左辺の変数が常に右辺の論理式の値を保持します.System Verilogではlogic型の変数に,Verilog 2001/1995ではwire型の変数に代入されます.一方,手続き代入文ではレグ型(reg)の変数に対して代入が行われ,ブロック内の変数の変化に応じて論理式が評価されます.この違いを理解することは,意図しないラッチ生成を避けるために重要です.

Verilogの代入方式と注意点

ブロッキング代入とノン・ブロッキング代入は,組み合わせ回路記述において重要な概念です.ブロッキング代入は「=」で表現され,上から順に代入が行われます.複数の代入文がある場合,記述順に影響し合うため,代入順序を意識して設計します.ノン・ブロッキング代入は「<=」で表現され,右辺を評価して一時記憶した後,まとめて左辺に代入する方式です.これにより代入順序に依存しない設計が可能です.

古いVerilog 1995では,always@(…)の括弧内にすべての入力信号を記述しなければ正しくシミュレーションされません.書き忘れると,該当変数が変化しても代入が実行されず,ラッチが生成される問題が発生します.Verilog 2001以降ではalways@*やSystem Verilogのalways_combを使用することで,こうした記述漏れによる不具合を防げます.

組み合わせ回路記述のポイント

- 継続代入文は左辺の変数に常時代入される

- 手続き代入文はスコープ内で右辺の変数が変化したときに代入が実行される

- ブロッキング代入は代入順序に依存する

- ノン・ブロッキング代入は順序に依存せず代入が行われる

- 古いVerilog 1995では入力信号の全列挙が必要

- Verilog 2001/System Verilogではalways@*やalways_combで簡潔に記述可能

System Verilogでは,assign文とalways_combの2つの方法が推奨されます.Verilog 2001でもassign文とalways@*が主流であり,Verilog 1995では入力信号の列挙に注意する必要があります.正しい代入方式を理解し,変数型の違いやラッチ生成のリスクを把握することで,意図とおりの組み合わせ回路を効率的に設計できます.

〈著:ZEPマガジン〉

参考文献

- Lチカ入門!ソフトウェア屋のためのHDL事はじめ,ZEPエンジニアリング株式会社.

- Zynqで作るカスタム・コンピュータ・チップ,ZEPエンジニアリング株式会社.

- [VOD/KIT]一緒に動かそう!Lチカから始めるFPGA開発【基礎編&実践編】,ZEPエンジニアリング株式会社.

- [VOD/KIT]Xilinx製FPGAで始めるHDL回路設計入門,ZEPエンジニアリング株式会社.

- [VOD/KIT]Zynqで初めてのFPGA×Linux I/O搭載カスタムSoC製作,ZEPエンジニアリング株式会社.

- [VOD]カメラ×ラズパイで一緒に!初めての画像処理プログラミング

- [VOD/KIT] 実習キットで一緒に作る!オープンソースCPU RISC-V入門,ZEPエンジニアリング株式会社.

- [VOD/KIT]ARM Cortex-A9&FPGA内蔵SoC Zynqで初体験!オリジナル・プロセッサ開発入門,ZEPエンジニアリング株式会社.