出力容量(Coss)は効率を悪化させる

SiC GaN FETの高速ドライブ回路設計

SiCの性能を引き出す 寄生容量とドライブ回路設計

|

|---|

|

図1 $C_{oss}$によりスイッチング時にエネルギが蓄積され,その蓄積エネルギはスイッチ動作時に損失として消費される.容量値の大きい素子を選ぶと,高速スイッチングにおいて不利に働く.画像クリックで動画を見る.または記事を読む.[提供・著]住谷 善隆 詳細:[VOD]小型&高出力!高効率電源設計のためのSiC/GaNトランジスタ活用 100の要点【セッション1】実験!SiC/GaN FETを高速かつ安全に駆動する回路設計技術 |

SiCやGaNといったワイドバンド・ギャップ半導体を用いたパワー・デバイスは,高速スイッチングが可能で,高効率化と小型化に大きく貢献します.しかし,これらの性能を十分に活かすには,内部に存在する寄生容量の影響を理解し,設計段階で適切に扱う必要があります.

寄生容量が及ぼすスイッチング損失

MOSFETには入力容量($C_{iss}$),出力容量($C_{oss}$),帰還容量($C_{rss}$)などの寄生容量が存在します.これらはSi時代から設計者にとって重要な指標でした.SiCやGaN FETも基本構造はMOSFETに近く,この寄生容量に起因する損失への配慮は変わらず必要です.特に高電圧領域になると,$C_{oss}$に関する考慮が設計の要点になります.

$C_{oss}$によりスイッチング時にエネルギが蓄積され,その蓄積エネルギはスイッチ動作時に損失として消費されます.このため,容量値が大きい素子を選定すると,高速スイッチングにおいて不利に働く場合があります.

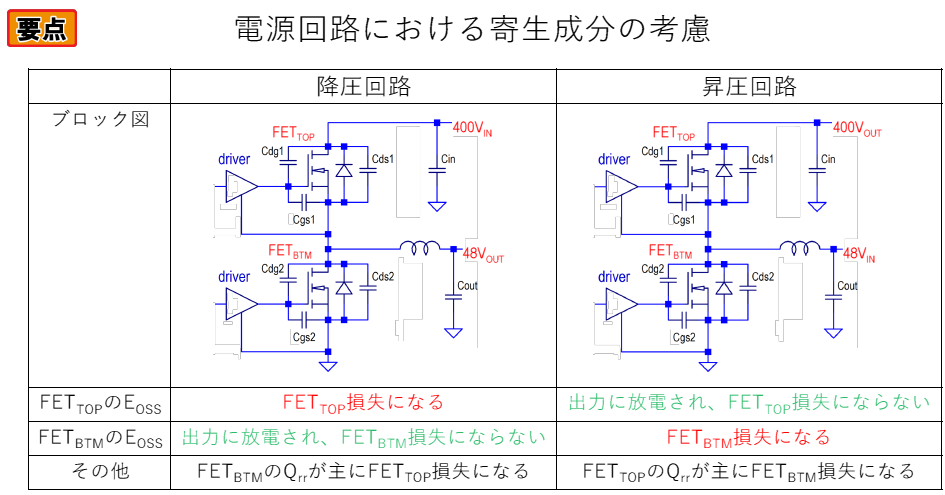

降圧回路と昇圧回路における損失分布

降圧回路と昇圧回路は基本構成は同じでも,スイッチング損失の発生箇所が異なります.

- 降圧回路では,高電圧から低電圧に変換するため,トップFETの$C_{oss}$が直接損失につながる

- 同時に,ボトムFETにおける出力容量は回路側にエネルギが流れるため,熱損失としてはカウントしない

- 逆回復電流($Q_{rr}$)はボトムFETで発生し,トップFETの損失を増加させる

一方で,昇圧回路では損失分布が逆転します.

- トップFETにおいては出力容量に関わる損失は発生しにくい

- ボトムFETに対し,$C_{oss}$損失と$Q_{rr}$損失が集中する

このように,同じトポロジであっても,動作条件により容量損失の位置と影響が変化します.そのため,デバイス選定や駆動方式の検討時には,寄生容量の性質と損失構造を考慮する必要があります.

設計時に考慮すべきこと

- SiCやGaN FETのデータシートに記載されている各容量値を確認する

- 使用するトポロジが降圧か昇圧かで,損失が集中するFETの位置を見極める

- ドライバ設計においては,容量に応じたゲート抵抗の設定とターンON/OFF時間の最適化が必要

高速スイッチング回路では,寄生容量による損失が大きく設計に影響します.特に高電圧回路では,容量損失の特性を踏まえたデバイス選定と熱設計が重要です.

まとめ

寄生容量による損失は,高速スイッチング素子であるSiCやGaNの性能を制限する要因です.回路トポロジと損失位置の関係を正しく理解し,適切な素子選定と熱設計を行うことが,高効率な電力変換回路設計における基本です.

出力容量Cossの意味とその影響

MOSFETにおける出力容量($C_{oss}$)は,ドレイン?ソース間の寄生容量であり,スイッチング時のエネルギ損失に直結します.この容量はFETがオフの状態でも蓄積される電荷に関係し,スイッチオン時にはそれがエネルギとして消費されるため,損失が発生します.

$C_{oss}$はドレイン?ソース間電圧によって変化し,特に高電圧領域では大きなエネルギを蓄積します.このため,高耐圧FETでは$C_{oss}$がスイッチング損失の主因となるケースも多く,高速化の足かせになることがあります.

回路トポロジ別の影響

- 降圧回路では,$C_{oss}$による損失は主にトップFETに集中する

- 昇圧回路では,逆にボトムFETの$C_{oss}$が損失源となる

- この損失は,熱設計時の重要なパラメータになる

容量が大きければ,より多くの電荷がスイッチオンのたびに消費されるため,スイッチング周波数が高い回路では無視できない損失になります.また,$C_{oss}$が大きいと,ターンオン時のドレイン電流の立ち上がりが遅れ,EMIやリンギングの原因になることもあります.

設計における対応策

- 素子選定時に$C_{oss}$値を確認し,用途に適した容量値のデバイスを選ぶ

- 駆動回路でのターンオン速度を制御することで過渡的な損失を抑える

- 並列接続時には,トータルの$C_{oss}$が加算されることに留意する

出力容量は見落とされがちなパラメータですが,実際には損失構造の中核を担う要素です.特にSiCやGaNを用いる際は,この値の扱い方が高効率回路の鍵を握ります.

まとめ

$C_{oss}$はMOSFETにおいてスイッチング損失を左右する重要な寄生容量です.動作トポロジと損失発生箇所の関係を把握し,適切な設計判断を行うことが,電力変換回路の信頼性と効率を両立させる基礎になります.

〈著:ZEPマガジン〉

著者紹介

- 2003年 パデュー大学大学院を卒業

- 2007年 リニアテクノロジー株式会社にFAEとして入社

- 2017年 アナログ・デバイセズ株式会社 車載ビジネス・デブロップメント・スペシャリスト.主に新製品の企画や開発に携わる

著書

- [VOD]小型&高出力!高効率電源設計のためのSiC/GaNトランジスタ活用 100の要点,ZEPエンジニアリング株式会社.

- [VOD]Before After!ハイパフォーマンス基板&回路設計 100の基本【パワエレ・電源・アナログ編】/【IoT・無線・通信編】,ZEPエンジニアリング株式会社.

- [VOD]Before After!ハイパフォーマンス基板&回路設計 100の基本【パワエレ・電源・アナログ編】,ZEPエンジニアリング株式会社.

参考文献

- [VOD]Before After!ハイパフォーマンス基板&回路設計 100の基本【パワエレ・電源・アナログ編】/【IoT・無線・通信編】,ZEPエンジニアリング株式会社.

- [VOD]Before After!ハイパフォーマンス基板&回路設計 100の基本【パワエレ・電源・アナログ編】,ZEPエンジニアリング株式会社.

- [VOD/KIT/data]一緒に作る!LLC絶縁トランス×超高効率・低雑音電源 完全キット,ZEPエンジニアリング株式会社.

- [VOD]高速&エラーレス!5G×EV時代のプリント基板&回路設計 100の要点,ZEPエンジニアリング株式会社.

- [VOD] Before After! ハイパフォーマンス基板&回路設計 100の基本【パワエレ・電源・アナログ編】/【IoT・無線・通信編】,ZEPエンジニアリング株式会社.

- [Book/PDF]デシベルから始めるプリント基板EMC 即答200,ZEPエンジニアリング株式会社.

- [VOD/KIT]ポケット・スペアナで手軽に!基板と回路のEMCノイズ対策 10の定石,ZEPエンジニアリング株式会社.

- [VOD]事例に学ぶ放熱基板パターン設計 成功への要点,ZEPエンジニアリング株式会社.

- [VOD]Pythonで学ぶ マクスウェル方程式 【電場編】+【磁場編】,ZEPエンジニアリング株式会社.