Si MOSFET内部の電流経路

SiC GaN FETの高速ドライブ回路設計

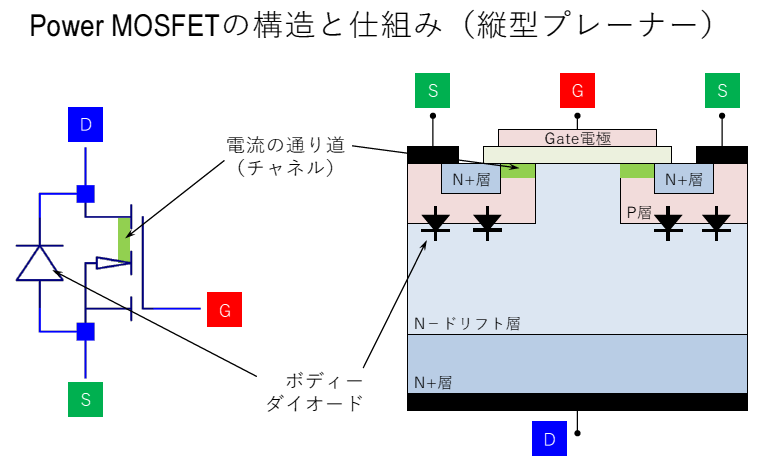

縦型構造パワーMOSFETの電流経路

|

|---|

|

図1 縦型構造パワーMOSFETの構造と電流経路 画像クリックで動画を見る.または記事を読む.[提供・著]住谷 善隆 詳細:[VOD]小型&高出力!高効率電源設計のためのSiC/GaNトランジスタ活用 100の要点【セッション1】実験!SiC/GaN FETを高速かつ安全に駆動する回路設計技術 |

パワーMOSFETは縦型プレーナ構造をもち,電流はソース(S)からドレイン(D)へ,シリコン基板の厚み方向に流れます.この縦型構造により,高耐圧を実現しながら,電流密度を高めることが可能です.

内部構造は上から順に,N+層,P層,N?ドリフト層,再びN+層という積層構成になっており,ゲート電極に電圧を印加することで,チャネルが形成され,電流が流れ始めます.

このとき,電流はチャネルを通ってP層を抜け,N?ドリフト層を経て下部のN+層へと移動します.ドリフト層の厚さと不純物濃度は耐圧に影響し,電界分布を最適化するための設計が重要です.

SiC・GaN FETにおける高速駆動回路のポイント

SiCやGaNベースのFETでは,立ち上がり・立ち下がり時間が極めて短く,高速スイッチングが可能です.この性質を活かすには,ドライブ回路側でも高速応答が必要です.

高速ドライブを実現するには,以下の要素が重要です.

- ゲート駆動電圧の最適化

- 低インピーダンスのゲート抵抗設計

- ゲートループの面積最小化によるノイズ抑制

SiCやGaNは高速動作時にリンギングが発生しやすく,電磁ノイズや誤動作を引き起こすことがあります.これに対処するために,ドライバICとFET間の距離を短くし,ゲート配線の寄生インダクタンスを最小限に抑えることが求められます.

チャネルからドレインまでの電流経路

Si MOSFETの電流は,まずゲートに印加される電圧によってP層にチャネルが形成され,ソース(S)から電流が流れ始めます.このチャネルはNチャネル型の場合,P層内に一時的にN型領域を作り,電子の移動を可能にします.

電流は形成されたチャネルを通過し,N?ドリフト層へ進みます.このドリフト層は,電界耐性を高めるために長く,抵抗成分である$R_{EPI}$を生じさせます.ドリフト層の厚みやドーピング濃度は,耐圧特性に直結する重要な設計パラメータです.

各抵抗要素と電力損失

MOSFETのオン抵抗$R_{DS(on)}$は,以下のような構成要素に分けられます.

- $R_{SUB}$:基板抵抗

- $R_{EPI}$:ドリフト層抵抗

- $R_{JFET}$:チャネル間隙抵抗

- $R_{CH}$:チャネル抵抗

これらの抵抗成分が合計されて,全体の導通損失が決まります.特に$R_{EPI}$は耐圧を高めるために不可避な存在ですが,導通損失の大部分を占めるため,Si MOSFETにおける性能トレードオフの中心です.

ボディー・ダイオードと破壊モード

MOSFETには寄生ダイオード(ボディー・ダイオード)が内在しており,オフ時に逆方向電圧が加わると,このダイオードが順方向に導通することがあります.

さらに,過剰な電界がドリフト層に加わると,ボディー・ダイオードがブレイクダウンし,デバイスが破壊に至る可能性があります.したがって,耐圧設計やクランプ回路の設置など,信頼性を高める設計が重要です.

〈著:ZEPマガジン〉

動画を見る,または記事を読む

著者紹介

著書

参考文献