想定外のVIAホール焼損

壊れない!壊さない!失敗だらけの電源・インバータ設計

VIAホール焼損防止のための電源設計技術

|

|---|

|

図1 VIAホールの焼損防止には,電流密度計算と熱設計が必要.許容電流は単純な断面積比ではなく,メッキ厚や熱拡散条件を考慮して算出する.画像クリックで動画を見る.または記事を読む.[提供・著]坂本 三直 詳細:[VOD]Before After!ハイパフォーマンス基板&回路設計 100の基本【パワエレ・電源・アナログ編】【セッション1】危険!高出力電源&インバータの安心設計 10の心得 |

大電流を扱う基板設計ではVIAホールの適切な設計が信頼性を左右します.焼損事故を防ぐための具体的な設計手法を解説します.

焼損発生のメカニズム

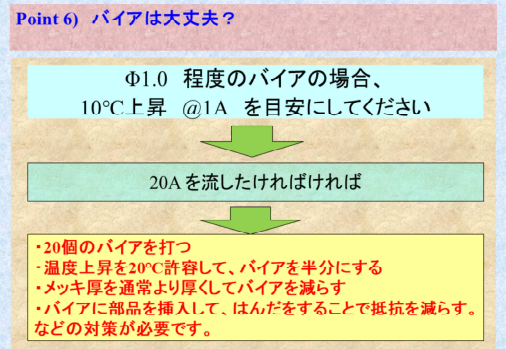

- 電流容量超過:直径1mmのVIAホール1個の許容電流は1A(銅メッキ厚15μm時)[2]

- 熱蓄積現象:10A流電時に20個必要なVIAを2個しか配置しない場合,理論上5倍の電流密度が発生

- 放熱経路不足:周辺パターン幅が狭く熱抵抗$R_{th}$が増大し,局所的な温度上昇を招く

設計対策の具体的手法

- VIA数計算式:$N = I_{max} / I_{via}$($I_{via}$:単体VIAの電流容量)

- メッキ厚管理:標準20μm→30μmに増加で電流容量1.5倍向上[1]

- 熱拡散設計:VIA周囲に幅3mm以上の銅箔パターンを放射状に配置

製造工程での注意点

- メッキ厚測定:断面研磨後,顕微鏡で25μm以上を確保

- はんだ充填:部品実装時にVIA内部をはんだで埋めることで接触抵抗を40%低減

- 熱応力テスト:-40℃~125℃の温度サイクルを100回実施し接続信頼性を検証

VIA設計の重要パラメータ

- アスペクト比:基板厚1.6mm時,推奨最大穴径0.3mm(5.3:1)[3]

- 熱抵抗計算:$R_{th} = d/($\lambda$A)$($d$:絶縁層厚さ,$\lambda$:熱伝導率)

- 信頼性向上:テーパードビア採用で機械的強度を30%増加[4]

動画を見る,または記事を読む〈著:ZEPマガジン〉〈著:ZEPマガジン〉〈著:ZEPマガジン〉〈著:ZEPマガジン〉

著者紹介

- 東京工業大学・大学院にてパワーエレクトロニクスの研究を行う.

- 1990年4月 パイオニア総合研究所にて液晶・有機ELの研究に従事.

- 1995年1月 大学時代の隣の研究室の博士とパワーエレクトロニクスの開発サポート

- 2010年10月 マイウェイプラス株式会社を退社後,株式会社デスクトップラボ設立 会社であるマイウェイ技研株式会社を設立.

著書

- [VOD]Before After!ハイパフォーマンス基板&回路設計 100の基本【パワエレ・電源・アナログ編】

参考文献

- [VOD]Before After!ハイパフォーマンス基板&回路設計 100の基本【パワエレ・電源・アナログ編】/【IoT・無線・通信編】,ZEPエンジニアリング株式会社.

- [VOD]Before After!ハイパフォーマンス基板&回路設計 100の基本【パワエレ・電源・アナログ編】,ZEPエンジニアリング株式会社.

- [VOD/KIT/data]一緒に作る!LLC絶縁トランス×超高効率・低雑音電源 完全キット,ZEPエンジニアリング株式会社.

- [VOD]高速&エラーレス!5G×EV時代のプリント基板&回路設計 100の要点,ZEPエンジニアリング株式会社.

- [VOD] Before After! ハイパフォーマンス基板&回路設計 100の基本【パワエレ・電源・アナログ編】/【IoT・無線・通信編】,ZEPエンジニアリング株式会社.

- [Book/PDF]デシベルから始めるプリント基板EMC 即答200,ZEPエンジニアリング株式会社.

- [VOD/KIT]ポケット・スペアナで手軽に!基板と回路のEMCノイズ対策 10の定石,ZEPエンジニアリング株式会社.

- [VOD]事例に学ぶ放熱基板パターン設計 成功への要点,ZEPエンジニアリング株式会社.

- [VOD]Pythonで学ぶ マクスウェル方程式 【電場編】+【磁場編】,ZEPエンジニアリング株式会社.