Zynqで初めてのFPGA×Linux I/O搭載カスタムSoC製作

開発環境の設定からプロセッサと自作IPの統合,高位合成,Linux上のCPUアプリ開発まで

(講義173分/314頁)

講師:森岡 澄夫 [インターステラテクノロジズ株式会社 シニアフェロー]

企画制作・主催:ZEPエンジニアリング株式会社

- 関連記事:Zynqで作るカスタム・コンピュータ・チップ

- 関連製品:[VOD/KIT]Xilinx製FPGAで始めるHDL回路設計入門

- 関連製品:[VOD/KIT]一緒に動かそう!Lチカから始めるFPGA開発【基礎編&実践編】

- 関連製品:[VOD/KIT] 実習キットで一緒に作る!オープンソースCPU RISC-V入門

- 関連製品:[VOD/KIT]ARM Cortex-A9&FPGA内蔵SoC Zynqで初体験!オリジナル・プロセッサ開発入門

ご購入

下記のボタンを押して,必要事項の入力をお願いいたします.

本セミナをお申込みされる前に

- [VOD]には,Cora Z7-07S Zynq-7000開発ボードが付属されていません.本ボードをお持ちの場合は,本VODの購入をご検討ください.

- 本製品は,2023年8月26日~27日に開催したウェビナを録画して編集した講義動画,テキスト,実習用ソースコードのセットです.講義動画は繰り返し再生,一時停止,巻き戻しが可能です.

- すべての映像,画像,文書テキスト,ソースコードは,著作権法によって厳格に守られています.無許可の転載,複製,転用は法律により罰せられます.

学ぶこと

ZynqはカスタムSoC(CPUとFPGA上の専用ハードを統合したシステム)を構築できる強力なチップですが,ソフト・ハードにまたがる多様な設計知識,とくにアーキテクチャ設計の知識が必要となるばかりか,開発ツールをセットアップしトラブルを解決しつつ使っていくのも独学では大変です.

本セミナでは,SoC設計に必要な知識や設計手法をおもにハード側の視点から説明するとともに,実機を動かしつつ開発環境の操作にも習熟します.

|

|---|

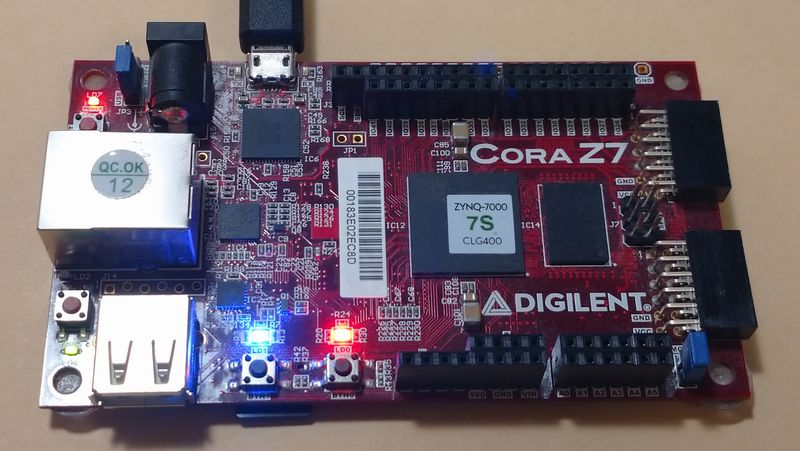

| 写真1 本セミナで使用するCora Z7-07S Zynq-7000開発ボード |

1日目

(1)環境セットアップ

~Vivado,Vitis,Windows用WSL,Ubuntuのインストール~

(2)カスタムSoCが役に立つ事例と製作の流れ

(3)アーキテクチャ設計に使う基礎知識・考え方

~CPU,専用ハード,オンチップバス~

(4)オンチップCPU(PS)を動作させる

~ブロック図作成ツールの操作~

(5)自作スレーブIPの統合

~プロセッサインターフェースの製作~

2日目

(6)自作マスターIPの統合

~データの流し方を考えてインターフェースを変える~

(7)ソフトコアCPU(MicroBlaze)の併用

~非対称マルチプロセッシングを試す~

(8)C言語からの回路合成機能を利用したIPコア作成

~複雑な処理の作成に向く高位合成を試す~

(9)Petalinuxのビルド環境構築とビルド

(10)Petalinux上のCPUアプリの開発

セミナで学ぶこと(Full Version)

ショートセミナ① 登場する基本パーツ

ショートセミナ② CPUと自作回路をつなぐ基本

ショートセミナ③ ツールによるブロック図作成の雰囲気

受講対象

- 業務などでZynqを使うことになった人

- SoCとは何で,製作に必要な知識が何かを知りたい人

- 設計に用いるツール群の操作を体感したい人

あると望ましい予備知識

- VerilogまたはVHDLによる簡単な回路設計経験

- C言語による簡単なマイコンプログラミング経験

- WindowsやLinuxの操作

講演の目標

- SoCの開発に用いる様々な基礎知識,とくにアーキテクチャ設計知識の取得

- マスタ/スレーブやデータ転送形式などに応じた,IP回路設計の基礎

- ベアメタル動作やOS(Linux,FreeRTOS)動作の体験

- ツール操作の体感や,操作上ミスしやすい事項の把握

実習に必要なパソコンやソフトウェア

- 講義テキストで別途指定するXilinx提供ソフトウェア(Vivado ML Edition Verion 2023.1&Patalinux 2023.1)などのダウンロード

- Windows OS,SSD(300GB以上の空き容量),メモリ32GB以上,プロセッサ最低3GHz程度のパソコン(推奨) ※低スペックでも動作するかもしれませんが,処理時間がかかります

- マイクロUSBケーブル

- 2GB以上のマイクロSDカード

講師紹介

略歴

NTT,IBM,Sony,NECの各研究所において高性能回路IPやハイレベルシンセシスの研究,およびプレイステーションなどの製品用SoC開発に従事した後,現職にて民間宇宙ロケットの飛行制御コンピュータの研究開発に従事.FPGAや高位合成を活用している.

主な著書

- HDLによる高性能ディジタル回路設計,CQ出版社.

- LSI/FPGAの回路アーキテクチャ設計法,CQ出版社.

- トランジスタ技術SPECIAL No.155 宇宙ロケット開発入門,CQ出版社.