正しく回路が生成されないHDL記述

文法やシミュレーションはOKでも安心できない

3つのNG記述とその理由

|

|---|

| 図1 回路化できないHDL記述その1.[著・提供]森岡 澄夫.画像クリックで動画再生.詳細は[VOD/KIT]Tiny FPGA実習!高校生から始めるHDLプログラミング |

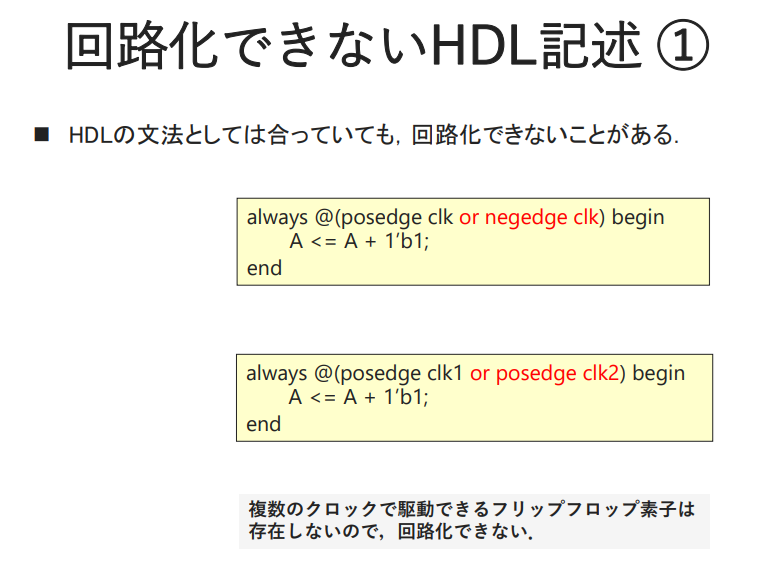

HDL(ハードウェア記述言語)は,ディジタル回路設計において不可欠なツールです.しかし,その記述が正しくても,必ずしも実際の回路に変換できるとは限りません. 例えば,複数のクロック信号で駆動されるフリップフロップは存在しないため,複数のクロックで同一の信号を駆動する記述は回路化できません.

組み合わせ回路内でループが発生している場合,回路として成立せず,シミュレーションはできても実際のハードウェアとしては動作しません. さらに,同一のレジスタに複数回代入する場合や,初期値が“always”ブロック外で設定されている場合も,回路化の際に問題となります.

これらの制約を理解し,正しいHDL記述を行うことが,実際に動作するディジタル回路を設計するためには欠かせません.

HDL記述が回路化できない理由はいくつかあります.

まず,複数のクロック信号で駆動されるフリップフロップは物理的に存在しないため,異なるクロックで同一のフリップフロップを駆動しようとする記述は回路化できません. このような記述を避けるためには,クロック・ドメインを明確に分離し,必要に応じてクロック・ドメイン間でのデータ転送を適切に行います.

次に,組み合わせ回路内でループが存在する場合,フィードバック・ループが形成され,出力が安定しない可能性があります.このような場合は,ループを解消するか,ラッチなどの適切な手法で回避します. また,同一レジスタに複数回代入する記述は,ツールによっては誤解釈されることがあり,予期しない動作を引き起こす可能性があります.このような場合は,代入の順序や条件を明確にし,誤解を招かないようにすることが重要です.

HDL記述を行う際には,これらの制約を十分に理解し,正しい回路設計を行うことが求められます.〈ZEPマガジン〉

著者紹介

- NTT,IBM,Sony,NECの各研究所において高性能回路IPやハイレベルシンセシスの研究,およびプレイステーションなどの製品用SoC開発に従事した後,現職にて民間宇宙ロケットの飛行制御コンピュータの研究開発に従事.FPGAや高位合成を活用している

著書

- [VOD/KIT]一緒に動かそう!Lチカから始めるFPGA開発【基礎編&実践編】,ZEPエンジニアリング株式会社.

- [VOD/KIT]Xilinx製FPGAで始めるHDL回路設計入門,ZEPエンジニアリング株式会社.

- [VOD/KIT]一緒に動かそう!Lチカから始めるFPGA開発【基礎編】,ZEPエンジニアリング株式会社.

- [VOD/KIT]Zynqで初めてのFPGA×Linux I/O搭載カスタムSoC製作,ZEPエンジニアリング株式会社.

- [VOD/KIT]Tiny FPGA実習!高校生から始めるHDLプログラミング,ZEPエンジニアリング株式会社.

- [VOD/Pi KIT]カメラ×ラズパイで一緒に!初めての画像処理プログラミング,ZEPエンジニアリング株式会社.

- スパコンでも破れない!高セキュリティ・マイコン・プログラミング,ZEPエンジニアリング株式会社.

- [YouTube]宇宙軌道ロケット 成功の方程式

- [YouTube]宇宙ロケットの電子回路開発

- FPGA/Zynqで作るカスタム・コンピュータ・チップ,ZEPエンジニアリング株式会社.

- Lチカ入門!ソフトウェア屋のためのHDL事はじめ,ZEPエンジニアリング株式会社.

- USBカメラの動画キャプチャ&描画用 Pythonプログラム,ZEPエンジニアリング株式会社.

- ライブラリ完備!組立式ラズパイI/O増設ボード MCC DAQ HATSファミリ誕生,ZEPエンジニアリング株式会社.