小型&高出力!高効率電源設計のための

SiC/GaNトランジスタ活用 100の要点

実用レベルに達した次世代パワー半導体のパフォーマンスを引き出す(講義263分/234頁)

- 著者・講師:住谷 善隆(Qorvo Japan有限会社) / 川口 正(SIGL代表) / 国峯 尚樹(株式会社サーマルデザインラボ) / 青木 弘利(株式会社タムラ製作所)/ 中野 利浩(サンケン電気株式会社)

- 企画編集・制作: ZEPエンジニアリング

- 本製品は,1人当たり1ライセンスです

- 関連製品:[VOD/KIT/data]一緒に作る!LLC絶縁トランス×超高効率・低雑音電源 完全キット

- 関連製品:[VOD/KIT/data]実験キットで学ぶ 電源・アナログ回路入門

- 関連製品:[VOD]高速&エラーレス!5G×EV時代のプリント基板&回路設計 100の要点

- 関連製品:[VOD] Before After! ハイパフォーマンス基板&回路設計 100の基本【パワエレ・電源・アナログ編】/【IoT・無線・通信編】

- 関連製品:[Book/PDF]デシベルから始めるプリント基板EMC 即答200

- 関連製品:[VOD/KIT]ポケット・スペアナで手軽に!基板と回路のEMCノイズ対策 10の定石

- 関連製品:[VOD]事例に学ぶ放熱基板パターン設計 成功への要点

お申し込み

下記のボタンを押して,必要事項の入力をお願いいたします.

| 内容 | テキスト | 視聴期間 | 税込価格 | 申し込み |

|---|---|---|---|---|

|

[録画] 小型&高出力!高効率電源設計のための SiC/GaNトランジスタ活用 100の要点 |

× | 1日 | \7,500 | |

|

[VOD] 小型&高出力!高効率電源設計のための SiC/GaNトランジスタ活用 100の要点 |

〇 | 無制限 | \9,900 |

お申込み前にご理解いただきたいこと

- 本VOD製品は,2024年4月19日に開催したオンライン・セミナ「小型&高出力!高効率電源設計のためのSiC/GaNトランジスタ活用 100の要点」を録画して編集した動画です.繰り返し再生,一時停止,巻き戻しが可能です.

- すべての映像,画像,文書テキスト,ソースコードは,著作権法によって厳格に守られています.無許可の転載,複製,転用は法律により罰せられます.

【セッション1】

実験!SiC/GaN FETを高速かつ安全に駆動する回路設計技術

容量性ゲートがスパッとON/OFFする高効率出力段の作り方

- 講師:住谷 善隆(Qorvo Japan有限会社)

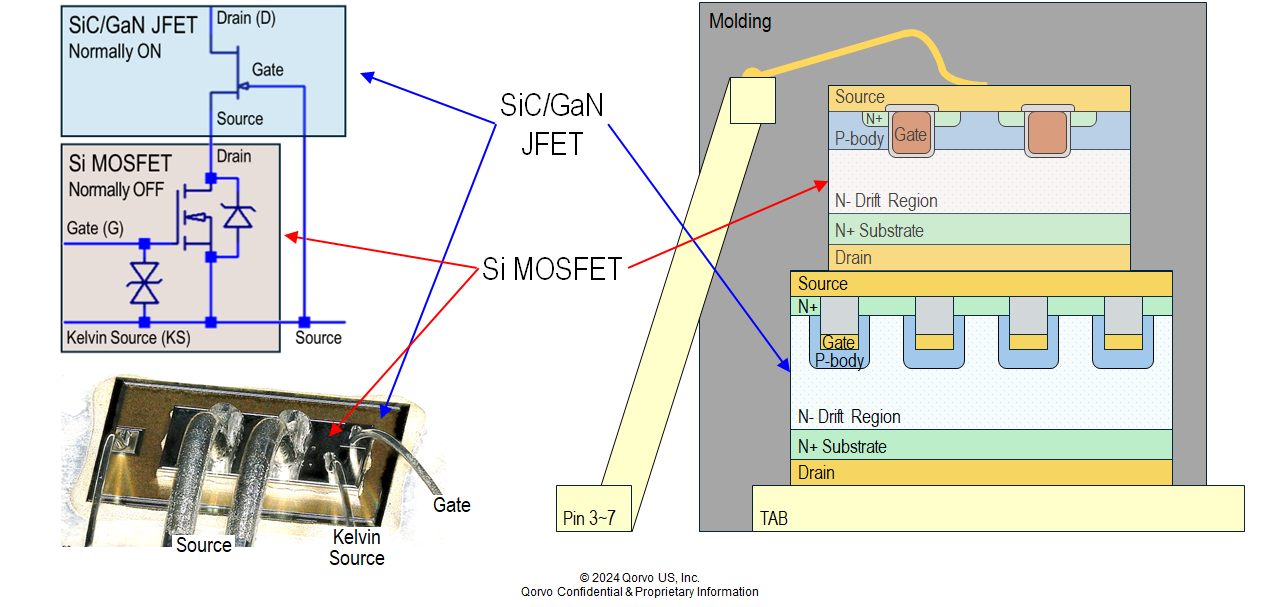

講演内容近年のSiC/GaNパワーデバイスは,SiC/GaN MOSFETとカスコードSiC/GaN FETに分類されます.カスコードSiC/GaN FETは,ノーマリ・オンのSiC/GaN JFETとノーマリ・オフのSi MOSFETをカスコード接続することで,ノーマリ・オフのSiC/GaN FETを実現しています. カスコードSiC/GaN FETは,Si MOSFETのシンプルな駆動回路で制御できる一方,スルー・レート制御が難しく,使いこなすにはGaN/SiCの寄生静電容量を考慮したゲート・ドライブ回路設計や基板設計が必要です.また,高性能な400V~1000Vを扱う高電圧回路の設計には,SiC/GaN MOSFETとカスコードSiC/GaN FETのそれぞれの特徴や特性を理解した上で,回路や使用条件に合わせて使い分けることも不可欠です. 本セッションでは,カスコードSiC/GaN FETの構造や動作原理を説明した後,回路シミュレーションを用いて,実際にSiC/GaNパワーデバイスを使いこなす回路設計テクニックを紹介します. 受講対象

講師紹介略歴

主な著書

|

【セッション2】

実験!EV用SiCインバータの数k~30MHz電磁界ノイズ対策 要点10

スマホや人体の暴露リスク低減!3相電流ルートやパスコン位置をシミュレーション解析

- 講師:川口 正(SIGL代表)

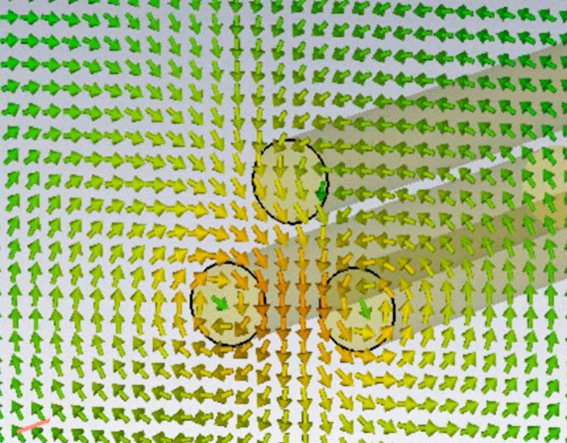

講演内容EV搭乗者の近くで,数k~30MHzの電磁ノイズを空間に放つ400V,20Aの3相モータが回っているEV関連では,高電圧・大電流を使用する電源とモータ間の配線の近くに人がいることから,数kHz程度までの空間電磁界漏洩量が,今後問題視されます. 従来のEMIの空間漏洩では,30MHz以上の基準が出されていますが,電子機器によってはすでに数k~30MHzの空間漏洩レベルも規制されています. 単相大電流では,電流の行きと戻りの配線(パターン)の間が離れないようにすることが基本ですが,3相の各配線に流れる電流には120°の位相差があり,最適な配線パターンはシミュレーションによって,その配置を探すのが賢明です. 30MHz以上のノイズは,スイッチング時の過渡電流による空間への漏洩電磁波が問題になりますが,スイッチング時のひげによるノイズの場合,3相の位相差で発生するわけではなく,各相ごとにノイズ対策をします.ただし,各相の線路ごとにシールドすると,3相の低周波成分間にシールドが入ってしまい,望ましくありません. 低周波成分が空間に漏洩しないようにするには,3相配線をまとめてシールドする必要があります.これらの点について,400V,20Aの3相モータを想定して,3Dシミュレーション結果を示しながら、総合的な電磁界漏洩対策について説明します. 低周波フルウェーブ解析機能で高電圧/大電流回路における電磁界のふるまいを正しく把握する数Hz~数十Hzの電磁界解析では,電界分布と磁界分布を独立して計算している場合が多いです.自動車のモータ駆動では各相数百Vの高電圧でかつ大電流が普通です.そのような系では電界と磁界ともに周囲への影響が大きいため,どちらかだけで解析すると回路から周囲空間への電磁的な影響を正しく把握できません. このような高電圧/高電流低周波回路では,電界と磁界を同時に計算できるフルウェーブ解析が必須です.世界的に定評ある3D電磁界シミュレータ CST Studio Suite(ダッソー・システムズ)は,低周波フルウェーブ解析機能を装備しています.本機能を活用すると,回路周辺の電界と磁界の解析が可能です. 本セッションの前半では,3相のケーブル配線と3相基板パターンの形状によって空間に漏えいする電磁界の状況を調べ,周囲への電磁界漏えいが少ない配線やパターンの構造を解析します. 低周波電流の分布を活用して適切なバイパス・コンデンサの配線パターンと配置を検討する電源回路やモータ制御回路などの基板設計では,銅パターンに通る低周波電流を水流でイメージして設計することが普通でした.これは,導体内の各部を進む電流の実測が困難であったことや,導体内部の電流分布解析シミュレーションのための適切なモデル/計算手法が進んでこなかったことが原因と考えられます. 本セッションの後半では,低周波電流が基板パターンのどの部分を通っているかをCST Studio Suiteで可視化し,バイパス・コンデンサを効果的に機能させるための基板パターンとコンデンサの配置を解析してみます. 受講対象

講師紹介略歴

主な著書

|

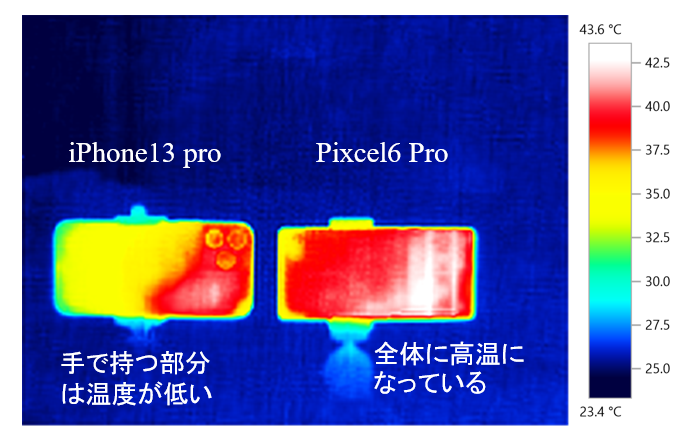

【セッション3】

実験!最新放熱技術と熱シミュレーションによる

SiC/GaNインバータの小型化 要点10

最新冷却デバイスの活用で容積を35%減!

- 講師:国峯 尚樹(株式会社サーマルデザインラボ)

講演内容パワー・デバイスの高出力化や集積回路の微細化,パッケージの小型化が進み,半導体デバイスの熱対策はますます難しくなっています. SiCやGaNなどの高発熱デバイスの冷却は,従来のヒートシンクやファンだけでなく,ヒート・パイプ,ベーパ・チャンバなどの新しい冷却デバイスが不可欠になっています.また高熱伝導の放熱材料との組み合わせにより,筐体への冷却機構とファンを組み合わせたハイブリット冷却も採用されています.さらに車載機器では環境温度が高いため,水冷機構を使用します. このように最近の冷却は多様化しており,発熱のレベルに応じた最適な冷却方式の採用が重要になっています.今回は,これら冷却方式の特徴,選定法などについて解説します. 受講対象

講師紹介略歴

主な著書

読みもの |

【セッション4】

GaN搭載ブリッジレスPFCとLLCコンバータで作る高効率電源設計事例

小型・高効率AC-DCコンバータの最新回路技術と実証結果

- 講師:青木 弘利(株式会社タムラ製作所)

講演内容GaN(窒化ガリウム)は,Si(シリコン)に比べ,スイッチング損失および導入損失の低減できるため,コンバータなどのスイツチング素子として使用すると効率が向上し,部品の小型化が可能です.また,LCAを含めた脱炭素化に貢献すると期待されており,注目を集めています.市場には,GaNを搭載したスイッチング電源やACアダプタも投入されています. 本セッションでは,AC-DCコンバータの高効率化を実現する回路技術であるブリッジレスPFCと,LLCコンバータにGaNを搭載をした場合の優位性についての実証結果をSi(Si-FET)と比較し,回路動作説明を交えながら解説します. 受講対象

講師紹介略歴

|

【セッション5】

電源効率改善のためのデジタル制御設計手法 要点10

ハードウェアとソフトウェアの融合による実用的なソリューション

- 講師:中野 利浩(サンケン電気株式会社)

講演内容一般的なAC電源を入力とする電子機器には高調波ノイズ対策として力率改善回路(PFC:Power Factor Correction)が必須であり,その高効率化にはさまざまな手法が用いられています. 高調波電流は,変圧器などへの過熱や騒音の原因になり,この対策に高調波電流規制があるため制限値以下に抑制することが求められていますので講義の中で説明いたします. 高効率化の手法には大きく分けて,回路方式や使用部品(SiC/GaN)などによるハードウェアとしての改善方法と,マイコンを使ったデジタル制御によるソフトウエアの改善方法があります. 本セッションでは,ハードウェアによる改善手法として,PFC回路の基本動作や,効率を改善するための様々な回路方式について説明します.また,ソフトウェアによる改善手法として,デジタル電源制御の基本動作からデジタル制御の特徴と応用例についても詳しく説明します. 最後に,実際のデジタル制御を用いたPFC電源についても紹介します. 受講対象

講師紹介略歴

主な著書

|